Jari Honkanen

# CONTROL DESIGN ISSUES IN GRID-CONNECTED SINGLE-PHASE CONVERTERS, WITH THE FOCUS ON POWER FACTOR CORRECTION

ACTA UNIVERSITATIS LAPPEENRANTAENSIS 920

Jari Honkanen

## CONTROL DESIGN ISSUES IN GRID-CONNECTED SINGLE-PHASE CONVERTERS, WITH THE FOCUS ON POWER FACTOR CORRECTION

Dissertation for the degree of Doctor of Science (Technology) to be presented with due permission for public examination and criticism in the Auditorium of the Student Union House at Lappeenranta–Lahti University of Technology LUT, Lappeenranta, Finland, on the 25<sup>th</sup> of September, 2020, at noon.

Acta Universitatis Lappeenrantaensis 920

| Supervisors | Professor Pertti Silventoinen<br>Applied Electronics<br>LUT School of Energy Systems<br>Lappeenranta–Lahti University of Technology LUT<br>Finland              |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Dr. Juhamatti Korhonen<br>Applied Electronics<br>LUT School of Energy Systems<br>Lappeenranta–Lahti University of Technology LUT<br>Finland                     |

| Reviewers   | Emeritus Professor Teuvo Suntio<br>Power Electronics<br>Department of Electrical Energy Engineering<br>Tampere University of Technology<br>Finland              |

|             | Professor of Practice Mikko Routimo<br>Power Electronics in Power Systems<br>Department of Electrical Engineering and Automation<br>Aalto University<br>Finland |

| Opponent    | Emeritus Professor Teuvo Suntio<br>Power Electronics<br>Department of Electrical Energy Engineering<br>Tampere University of Technology<br>Finland              |

|             | ISBN 978-952-335-547-7<br>ISBN 978-952-335-548-4 (PDF)<br>ISSN-L 1456-4491<br>ISSN 1456-4491                                                                    |

## Lappeenranta–Lahti University of Technology LUT LUT University Press 2020

## Abstract

Jari Honkanen Control design issues in grid-connected single -phase converters, with the focus on power factor correction Lappeenranta 2020 92 pages Acta Universitatis Lappeenrantaensis 920 Dissertation, Lappeenranta–Lahti University of Technology LUT ISBN 978-952-335-547-7, ISBN 978-952-335-548-4 (PDF) ISSN-L 1456-4491, ISSN 1456-4491

Electrical equipment is most commonly powered from a mains connection. The mains alternating voltage is rectified, isolated, and regulated in a power supply. The power supply acts as an interface between the mains voltage and the powered equipment. In addition to protecting the equipment from the mains voltage, the power supply isolates the mains connection from the distortions of the powered equipment. The protection against distortion is accomplished by controlling the voltages inside the power supply and the shape of the current drawn from the mains.

In many cases, the simplest control loop design will suffice, but a more elaborate control loop design is usually needed to meet all the design requirements. The current loop performance of the digitally controlled power factor correction is improved with a simple feedforward term. The idea for the proposed solution stems from the Lyapunov control theory.

The voltage loop performance of the power factor correction is improved by using a fuzzy nonlinear controller. The controller is simple to implement, as the underlying solution is to schedule the gains of two different PI controllers with the error between the measurement and the reference. Application of the presented controller simplifies the control design as the control designs for the steady-state and transient performance are decoupled, allowing the control to yield a fast transient with a low distortion, which are typically mutually exclusive. With a linear control, the dynamics of the DC link is a choice between a low distortion and a fast transient performance.

Further, this doctoral dissertation discusses the benefit of a digital control

platform with the option to optimize the feedback measurement. The idea of proper timing of the current measurement, thereby minimizing the effects of anti-alias filtering, is investigated in the case of current measurement in a grid-forming inverter. The benefit of the proper timing of the measurement and filter design is a reduction in noise by -20 dB in the current measurement with a minimal phase delay.

All of the results obtained in the study were verified by extensive experimental measurements to validate the achieved performance and show that the algorithms and methods provide benefits in an actual setting.

Keywords: digital control, power electronics, power factor correction

## Acknowledgments

I want to express my gratitude to Mr. Samuli Räisänen as the head of the Powernet project as well as his role to introducing me to the world of power electronics and the fantastic people in it. I also want to thank my former colleagues Mikael Tötterman and Pasi Lauronen and rest of the wonderful people of Efore Oyj. I truly enjoyed my brief time in Espoo working with some of the best engineers in the field of power electronics.

I want to thank the reviewers Professor Teuvo Suntio and Professor Mikko Routimo. Your efforts have greatly improved this dissertation.

Special thanks to Professor Pertti Silventoinen. It was a pleasure to work under you guidance.

I want to thank my supervisor and good friend Dr Juhamatti Korhonen for your endless support with the research, writing and your boundless patience. Special thanks also belong to the original project group Dr Juha Ström and Dr Janne Hannonen. There could not have been a better research group than you two. Some of the best times I have ever had were spent working with the rest of the original gang of 6405, Dr Juho Tyster, Dr Arto Sankala, Dr Mikko Qvintus, Dr Tommi Kärkkäinen and mr Saku Levikari.

I want to thank all my current colleagues and friends. You all have made work something to look forward to. I wish to especially thank Jussi Karttunen for the many interesting conversations. And of course for your part in getting me into the many ways extra special place that is Danfoss Editron. I also tip my hat to the new class of 6405, it is a pleasure to see that the people and locations may change but the spirit remains the same. As spoken by Zarathustra "I say unto you: one must still have chaos in oneself to be able to give birth to a dancing star."

I will always be grateful to Dr. Hanna Niemelä for her efforts to improve the language of this dissertation.

I want to express my deepest gratitude to the best parents anyone could hope for, Aila and Keijo and my sister Emppu. More overly protective parents would have thought of a mains connected tube amplifier to be too dangerous and difficult first project for a child with no prior knowledge of anything related to electronics.

Finally I want to thank my family Aino and Essi. You two are my bringers of joy and mscd.x

Jari Honkanen September, 2020 Lappeenranta, Finland Two things I know that are true: 1. Nothing in this world has ever been done as well as it could have been and 2. Nothing in this world needs to be done \textfb{that} well done!

Yours, Jari

# Contents

Abstract

| Acknowledgments                      |         |                                  |                                                         |    |  |  |

|--------------------------------------|---------|----------------------------------|---------------------------------------------------------|----|--|--|

| Contents                             |         |                                  |                                                         |    |  |  |

| List of Symbols and Abbreviations 11 |         |                                  |                                                         |    |  |  |

| Lis                                  | st of p | ublicati                         | ions                                                    | 15 |  |  |

| 1                                    | Intro   | duction                          | 1                                                       | 17 |  |  |

|                                      | 1.1     |                                  | factor                                                  | 18 |  |  |

|                                      | 1.2     |                                  | electronics circuits for an AC interface                | 20 |  |  |

|                                      |         | 1.2.1                            | Boost PFC                                               | 21 |  |  |

|                                      |         | 1.2.2                            | Single-phase inverter                                   | 21 |  |  |

|                                      |         | 1.2.3                            | Power-factor-corrected power supply                     | 22 |  |  |

|                                      |         | 1.2.4                            | PFC control                                             | 22 |  |  |

|                                      |         | 1.2.5                            | DCM operation of the PFC                                | 25 |  |  |

|                                      |         | 1.2.6                            | Current measurement                                     | 25 |  |  |

|                                      | 1.3     | Digital                          | hardware in power electronics                           | 27 |  |  |

|                                      |         | 1.3.1                            | Digital control platforms used in the study             | 29 |  |  |

|                                      | 1.4     | Scope and motivation of the work |                                                         | 30 |  |  |

|                                      |         | 1.4.1                            | Digital control platform                                | 31 |  |  |

|                                      |         | 1.4.2                            | Improvements in the current control                     | 32 |  |  |

|                                      |         | 1.4.3                            | Improvements in the voltage control                     | 33 |  |  |

|                                      |         | 1.4.4                            | Dual sampling inverter control measurements             | 34 |  |  |

|                                      | 1.5     |                                  | ch methods and scientific contributions of the doctoral |    |  |  |

|                                      |         | disserta                         |                                                         | 35 |  |  |

|                                      | 1.6     | Structu                          | re of the doctoral dissertation                         | 35 |  |  |

| 2                                    | PFC     | control                          | design                                                  | 37 |  |  |

|                                      | 2.1     | Power                            | factor control hardware used in the study               | 38 |  |  |

|                                      | 2.2     | Constru                          | action of the input current controller                  | 39 |  |  |

|                                      |         | 2.2.1                            | Simplifying the feedback controller                     | 41 |  |  |

|                                      |         | 2.2.2                            | Control tuning                                          | 42 |  |  |

|    |                                 | 2.2.3    | Effect of the DC link voltage on the inductor current  |    |  |

|----|---------------------------------|----------|--------------------------------------------------------|----|--|

|    |                                 |          | control                                                | 43 |  |

|    | 2.3                             | Nonlir   | near DC link voltage control                           | 44 |  |

|    |                                 | 2.3.1    | DC link control design                                 | 47 |  |

|    |                                 | 2.3.2    | Voltage control tuning                                 | 50 |  |

|    |                                 | 2.3.3    | Controller stability                                   | 53 |  |

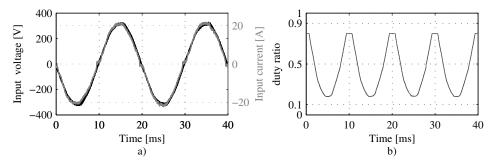

|    | 2.4                             | Experi   | imental results                                        | 55 |  |

|    |                                 | 2.4.1    | Nonlinear DC link voltage control measurements         | 56 |  |

|    | 2.5                             | Discus   | ssion on the PFC voltage and current controls          | 61 |  |

| 3  | Con                             | trol des | sign of a single-phase inverter considering improved   |    |  |

|    | timi                            | ng of th | ne measurement                                         | 63 |  |

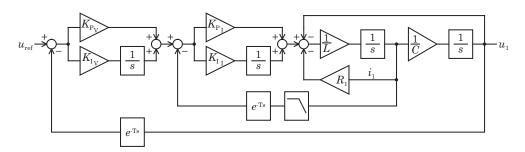

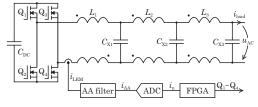

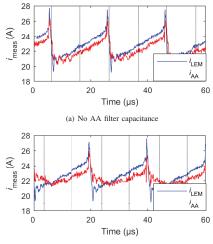

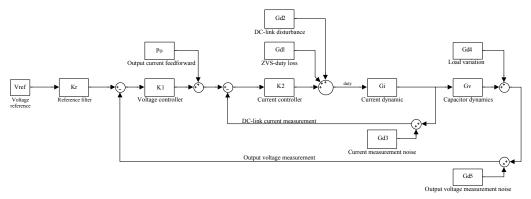

|    | 3.1                             | Single   | -phase inverter control                                | 65 |  |

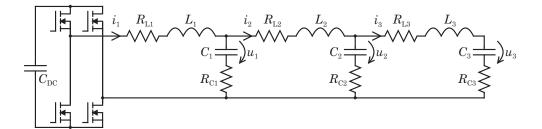

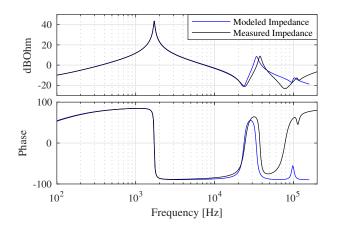

|    |                                 | 3.1.1    | Modeling of a single-phase inverter with an EMI filter | 66 |  |

|    |                                 | 3.1.2    | Inverter feedback control                              | 69 |  |

|    | 3.2                             | Contro   | bl design                                              | 70 |  |

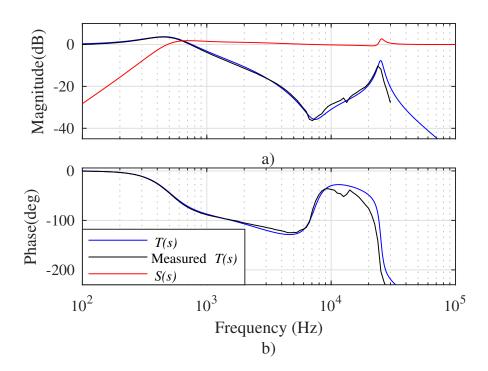

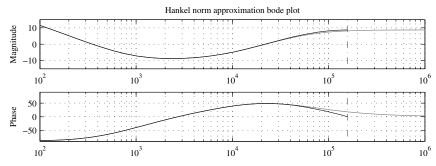

|    |                                 | 3.2.1    | Sensitivity of the cascaded PI control                 | 72 |  |

|    |                                 | 3.2.2    | Tuning of the cascaded control                         | 73 |  |

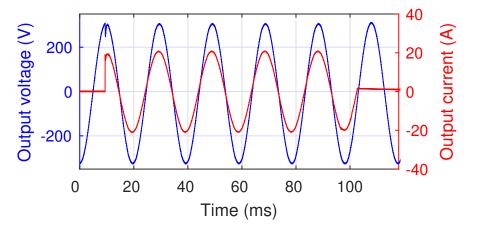

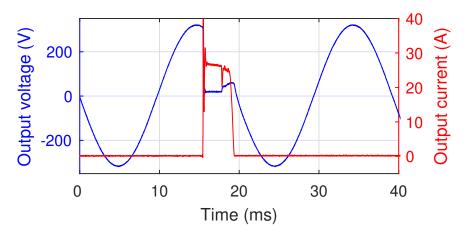

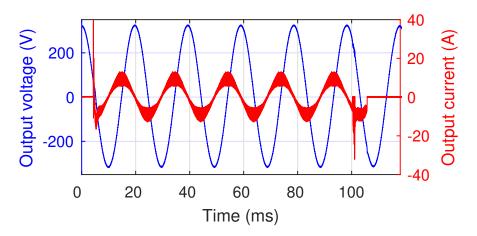

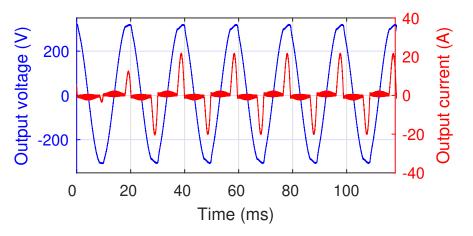

|    | 3.3                             | Experi   | imental measurements                                   | 76 |  |

|    |                                 | 3.3.1    | Discussion on dual sampling and control                | 78 |  |

| 4  | Conclusions and future research |          |                                                        | 81 |  |

|    | 4.1                             | Sugge    | stions for future work                                 | 82 |  |

| Re | References 8                    |          |                                                        |    |  |

## **Publications**

# **List of Symbols and Abbreviations**

## Latin alphabet

- d(t) controlled duty ratio

- e(t) control error

- $i_1$  switch 1 current measurement

- K<sub>1</sub> set of control gains for the first membership function

- K<sub>i</sub> integrator gain

- K<sub>p</sub> proportional gain

- L inductance

- S(s) sensitivity function of a closed-loop system

- T(s) tracking function of a closed-loop system

- u voltage

- V(t) Lyapunov function

## Greek alphabet

- $\Delta(t)$  Additive disturbance signal

- $\omega$  angular frequency

- $\omega(t)$  integrator state in a controlled system

- $\varphi$  voltage phase

- $\phi$  current phase

## **Subscripts**

- $f_{AA}$  anti-aliasing cutoff frequency

- $f_{\rm ctrl}$  control frequency

| $f_{\rm out}$           | output frequency                        |  |

|-------------------------|-----------------------------------------|--|

| $f_{\rm s}$             | current sampling frequency              |  |

| $f_{\rm sw}$            | switching frequency                     |  |

| In                      | n:th current harmonic                   |  |

| V <sub>RMS</sub>        | root-mean squared voltage               |  |

| $M_1$                   | first membership function               |  |

| $m_1$                   | lower limit for the membership function |  |

| m <sub>2</sub>          | upper limit for the membership function |  |

| Paverage Average power  |                                         |  |

| ref                     | reference                               |  |

| Т                       | mains cycle period                      |  |

| <i>t</i> <sub>ADC</sub> | AD conversion time                      |  |

| t <sub>DT</sub>         | dead time                               |  |

| <i>u</i> <sub>AC</sub>  | output voltage                          |  |

| u <sub>ref</sub>        | reference voltage                       |  |

| $V_n$                   | n:th voltage harmonic                   |  |

| <i>I</i> <sub>RMS</sub> | root-mean squared current               |  |

| Abbreviations           |                                         |  |

| AA                      | anti-aliasing (filter)                  |  |

| AC                      | alternating current                     |  |

| ADC                     | analog-to-digital converter             |  |

| CCM                     | and in the second second                |  |

- CCM continuous current mode

- DC direct current

- DCM discontinuous current mode

- DPF displacement power factor

- DSP digital signal processor

- EMI electromagnetic interference

- FPGA field programmable gate array

- GaN gallium nitride

- IGBT insulated gate bipolar transistor

- MHz megahertz

- MOSFET metal oxide field effect transistor

- PF power factor

- PF<sub>D</sub> distortion power factor

- PFC power factor correction

- SiC silicon carbide

- THD total harmonic distortion

- T-S Takagi-Sugeno

- ZOH zero-order hold

## List of publications

The results of the study are documented in a scientific journal and peerreviewed conference publications. This doctoral dissertation consists of the following publications.

#### **Publication I**

Honkanen, J., Hannonen, J., Silventoinen, P., and Räisänen, S. (2015), "Single phase PFC control with Lyapunov method," in *17th European Conference on Power Electronics and Applications EPE'15 ECCE-Europe*, Geneva, Switzerland, pp. 1–5.

#### **Publication II**

Honkanen, J., Hannonen, J., Korhonen, J., Nevaranta, N., and Silventoinen, P. (2018), "Nonlinear PI-control approach for improving the DC link voltage control performance of a power factor corrected system," *IEEE Transactions on Industrial Electronics*, Vol. 66, Iss. 7, July 2019, pp. 5456–5465.

#### **Publication III**

Korhonen, J., Honkanen, J., Rautio, J., and Silventoinen, P. (2019), "Effect of Current Measurement Timing and Antialiasing Filter in a Single-Phase Inverter," in *Proceedings of IEEE Applied Power Electronics Conference and Exposition*, Anaheim, CA, USA, pp. 938–943.

#### **Publication IV**

Hannonen, J., Ström, J. P., Honkanen, J., S. Silventoinen, P., Räisänen, S. and Pokkinen, O. (2013), "Design of digitally controlled isolating 1-phase AC/DC converter by using centralized processing unit," in *15th European Conference on Power Electronics and Applications (EPE)*, Lille, France, pp. 1–10.

### **Author's contribution**

In Publication I, Mr. Honkanen was the principal author of the paper and the main contributor to its scientific content. Mr. Honkanen developed the algorithm, constructed the experimental setup for the measurements, and executed the empirical experiments and simulations. The software for the experimental device was written mostly by Dr. Hannonen. Dr. Korhonen and Dr. Nevaranta helped with writing and commented on the paper.

In Publication II, Mr. Honkanen was the principal author of the paper and the main contributor to its scientific content. Dr. Hannonen took part in conducting the experiments with the author. Mr. Räisänen and Prof. Silventoinen provided comments on the paper.

In Publication III, Mr. Honkanen was responsible for the design and construction of the experimental device. These tasks covered dimensioning of the magnetic components, winding of the transformers and the inductors, design of the PCBs for the inverter and the FPGA platform, design of the embedded system, and development of the embedded hardware and software. Mr. Honkanen was also responsible for the design of the measurements and the sampling algorithm.

In Publication IV, Mr. Honkanen was the coauthor responsible for the design of the control and the signal processing used for conditioning of the measurements. Mr. Honkanen was also responsible for all of the modeling work and took part in the debugging of the experimental device. The schematic of the experimental device was designed by Dr. Hannonen, who together with Dr. Ström was also responsible for the software design of the embedded platform. All of the authors were responsible for the design of the experimental setup and measurements.

# 1 Introduction

Power electronics is a field of engineering that focuses on the control and conversion of electrical energy. The control of power supplies is implemented with semiconductors that are switched on and off at a rate from thousands to millions of times per second to produce high-frequency voltage pulses to control the energy flow. The use of high switching frequencies allows compact conversion systems still reaching efficiencies of 98–99% (Badstuebner et al., 2010; Rothmund et al., 2019; Radimov et al., 2020).

Most electronic devices are powered from the mains. In a typical power supply, the AC mains voltage is first rectified before further processing by switch mode converters is possible. This applies to all kinds of systems, such as battery chargers (Yilmaz and Krein, 2013), communication towers (Badstuebner et al., 2010), and computers (Singh et al., 2016), all of which run on DC power processed by switch-mode power supplies. The main problem with power supplies is the electromagnetic interference (EMI) that they cause and the nonlinear loading that they present to the mains (Mainali and Oruganti, 2010).

Nonlinear loads disrupt and interfere with the mains voltage, and thus, also with other equipment that shares the same mains connection (Mainali and Oruganti, 2010). The disruption is the result of nonlinear loads drawing nonsinusoidal current from the mains. The distorted, harmonic-rich currents interact with the impedance of the mains connection, introducing harmonics to the mains voltage waveform and thus distorting the mains voltage (Faiz et al., 2015). The harmonic currents also cause extra heating in the distribution transformer windings and cores, thereby increasing the losses in the distribution network (Faiz et al., 2015). Compared with a pure sine shape, the distorted current also increases the peak current drawn from the mains connection for a given power level.

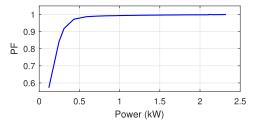

## **1.1** Power factor

In an effort to limit the ill effects of nonlinear loads in the mains-connected equipment, standards have been established for the quality of power drawn from the mains (IEC61000-3-2, 2009). The standard limits the allowed harmonic currents to acceptable levels, and most mains-powered devices have to adhere to these limits. In order to properly interface a nonlinear power electronic load to the mains, the quality of the current drawn from the mains has to be corrected. This quality of the mains current is called the power factor.

Power factor is defined as

$$PF = \frac{P_{average}}{I_{RMS} \cdot V_{RMS}}.$$

(1.1)

The mean value of the product of voltage and current over an interval of one mains cycle T is obtained by the ratio of average power  $P_{\text{average}}$  to RMS power

$$P_{\text{average}} = \frac{1}{T} \int_0^T v(t) i(t) dt. \qquad (1.2)$$

As the mains voltages and currents are periodic, the waveforms can be decomposed into the mains frequency fundamental signal and its integer multiples using a Fourier series

$$v(t) = V_0 + \sum_{n=1}^{\infty} V_n \cos\left(n\omega t - \varphi_n\right)$$

(1.3)

$$i(t) = I_0 + \sum_{n=1}^{\infty} I_n \cos\left(n\omega t - \phi_n\right), \qquad (1.4)$$

where  $\varphi$  and  $\phi$  are the phases of specific harmonic components of voltage and current waveforms. The average power can be obtained by substituting (1.3) and (1.4) into (1.2)

$$P_{\text{average}} = \frac{1}{T} \int_0^T \left( V_0 + \sum_{n=1}^\infty V_n \cos\left(n\omega t - \varphi_n\right) \right) \left( I_0 + \sum_{n=1}^\infty I_n \cos\left(n\omega t - \varphi_n\right) \right) dt.$$

(1.5)

As mentioned in (Erickson and Maksimovic, 2001), calculating the integral (1.5) yields

$$P_{\text{average}} = V_0 I_0 + \sum_{n=1}^{\infty} \frac{V_n I_n}{2} \cos\left(\varphi_n - \phi_n\right). \tag{1.6}$$

On the other hand, taking the root mean square value of (1.3) and (1.4) yields

$$V_{\rm RMS} = \sqrt{V_0^2 + \sum_{n=1}^{\infty} \frac{V_n^2}{2}}$$

(1.7)

$$I_{\rm RMS} = \sqrt{I_0^2 + \sum_{n=1}^{\infty} \frac{I_n^2}{2}}.$$

(1.8)

As noted in (Erickson and Maksimovic, 2001), the significance of the phase present in (1.6) is that only the harmonic components that have a correct phase relationship add to the average power delivered to the load. This is in contrast to RMS values (1.7) and (1.8), as all the harmonics increase the RMS value regardless of the phase.

A power factor of 1 thus requires that the RMS and average values of the current and voltage signals are equal. This is achieved when the current and voltage waveforms have the same harmonic content with a matching phase relationship (Erickson and Maksimovic, 2001). In the case that the mains voltage is not carrying harmonics, a high power factor requires that the mains current is free from both reactive currents and current harmonics.

When nonlinear loads are used, a high power factor can be achieved by filtering the mains current with either passive filters, by using capacitive and inductive components, or actively with power electronics. The main issue with passive harmonic filtering is that the filters are expensive and large because of the low-frequency mains harmonics that need to be filtered (Singh et al., 2003). When power electronics are used to filter the harmonics, only the high switching frequencies have to be filtered passively (Rossetto et al., 2000). This allows the use of small electromagnetic interference (EMI) filter components designed to filter out the high switching frequencies (Liu et al., 2013) in the range of tens to hundreds of kiloherz. The EMI filter has capacitance that draws reactive current; however, as the EMI filter components are dimensioned to be effective for the kHz to MHz range, they have a limited effect on the 50–60 Hz mains frequencies. Thus, in a power electronics system, the harmonic currents typically have the most adverse effect on the system and are of the highest concern (Levron et al., 2014).

In a mains-powered device, such as a charger or a computer power supply, the harmonic currents are controlled with a dedicated power electronics circuit called the power factor correction, or in short, PFC.

## **1.2** Power electronics circuits for an AC interface

An active power factor correction can be accomplished with various power electronics circuits. A commonly used circuit is a boost converter, but also Cúk, flyback, and single-ended primary-inductor (SEPIC) converters are used to provide the PFC function (Fardoun et al., 2012), (Bist and Singh, 2015), (Jovanovic and Jang, 2005). With wide band gap devices, a totem-pole converter can also be effectively used for the PFC. It is, however, not practical with silicon devices because of the hard switching losses in a half bridge (Huang and Huang, 2017).

In single-phase systems, power factor correction is most commonly achieved with a boost converter. The choice of the boost converter is obvious as it has a low component count, it is simple to control, and the switch is easy to drive (Brown, 2001).

### **1.2.1 Boost PFC**

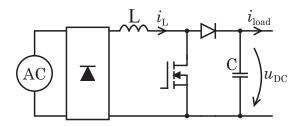

The boost converter is depicted in Figure 1.1. The mains voltage is rectified by using a diode rectifier, and the full-wave-rectified voltage is then interfaced to the DC link voltage with a boost converter. The boost converter is controlled to produce the current that tracks the mains voltage waveform. This operation minimizes the effect of the nonlinear current on the mains voltage (Orabi and Ninomiya, 2003).

Typical variations of the boost PFC configurations are single and parallel boost converters and a bridgeless boost converter. Bridgeless and parallel boost converters, in particular, are used for higher power levels because of the distribution of the losses between several devices (Singh et al., 2003).

Bridge configurations with four switches are used when the direction of the power has to be reversed, for example in active filters and uninterruptible power supplies (Erickson and Maksimovic, 2001). In these kinds of applications, the PFC is also referred to as an active front end.

### **1.2.2** Single-phase inverter

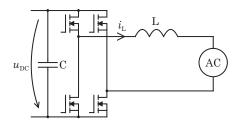

The main components of the inverter are shown in Figure 1.2. The four transistors are used to provide a pulse-width-modulated voltage, which is then filtered with an appropriate passive filter. If the inverter is connected to the grid, it can draw or supply the grid with sinusoidal current, thereby acting as a PFC to the current being fed or drawn from the grid.

In grid-forming operation, the inverter is required to support any load that is typically powered from mains voltage, and it should thus provide steady sine voltage under linear and nonlinear load voltages at the  $u_{DC}$  node. There are standards that define the dynamical performance requirements for single-phase inverters used to supply AC voltage as well as limits for allowed electromagnetic emissions (IEC-62040-3, 2014).

Figure 1.1. Single switch boost converter; the most common power factor correction topology in single-phase systems.

Figure 1.2. Single-phase inverter.

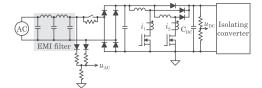

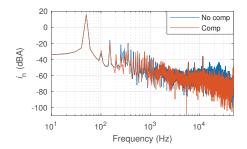

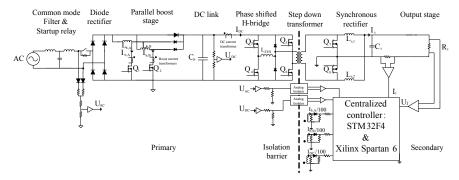

## 1.2.3 Power-factor-corrected power supply

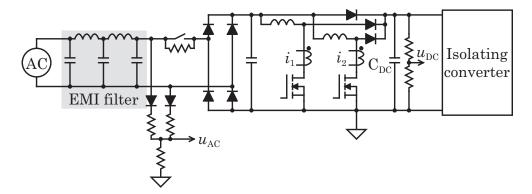

As most devices are required to have a PFC, a basic power supply has three main parts: an EMI filter, a rectifier, and a DC/DC converter. An example of a power-factor-corrected power supply is shown in Figure 1.3. The load is fed from the rectified voltage by a DC/DC converter, which provides voltage level conversion and galvanic isolation, and the PFC stage ensures a proper mains connection without excessive interference to the grid. Therefore, the PFC acts as an interface between the DC/DC stage and the mains voltage by eliminating the adverse effects of the nonlinearities and the resulting harmonics from the mains. As described for example in (Wu, 2006), the boost in the PFC cannot have an appropriate power factor without changing the switch duty cycle. For this reason, the mains current has to be actively controlled with a feedback.

## 1.2.4 PFC control

The PFC control has two main objectives: It controls the input current waveform and the level of the rectified DC voltage. Because the DC link voltage

Figure 1.3. Structure of the parallel boost PFC. The main components are the EMI filter, two identical boost converters in parallel, and an isolating converter that translates the DC link voltage into the required voltage level. The figure also shows the placements of the measurements used for the feedback control. The switch currents  $i_1$  and  $i_2$  are measured with current transformers,  $u_{AC}$  is the rectified grid voltage measurement, and  $u_{DC}$  is the DC link voltage measurement.

level, which is the output of the PFC, is regulated, the power supplies that draw power from it work at relatively constant input voltages. This enables a higher efficiency as the controlled DC link voltage ensures more consistent operating conditions for the rest of the power circuits. Because the boost PFC provides a regulated DC link, it can be designed to work with different mains voltages and frequencies (Jang and Jovanovic, 2009), with possibly a derated power level.

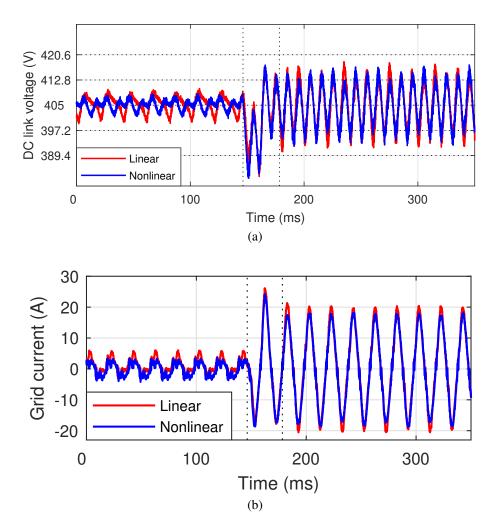

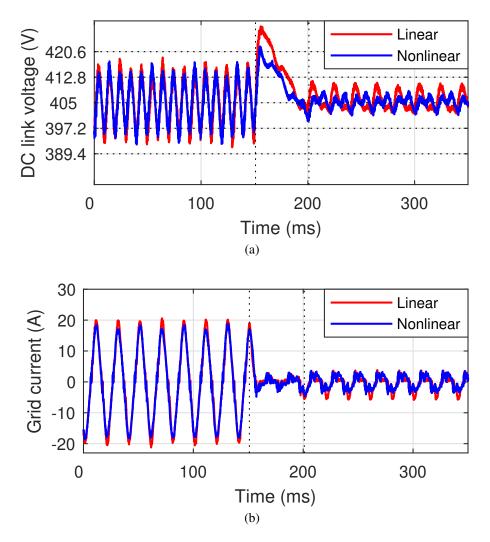

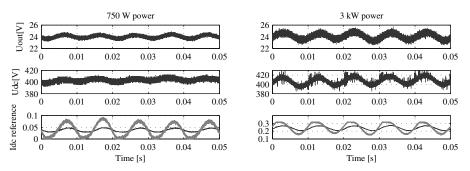

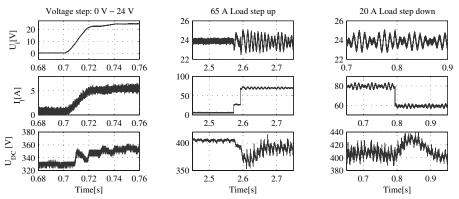

As the PFC controls the level of the rectified DC voltage along with the input current waveform, an appropriate PFC control has to provide fast regulation of the DC link voltage. The performance of the DC link regulation is usually evaluated by the time it takes for the DC link to stabilize from a load step. A PFC should ensure a minimal voltage sag when the load is stepped up with a fast return to the nominal voltage level.

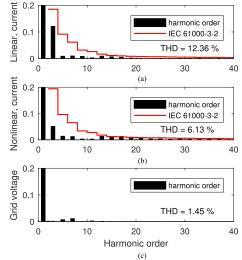

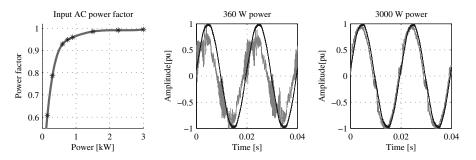

As the THD is a measure of the quality of current drawn from the mains, the THD is also a measure of the performance of a PFC. The THD of the drawn mains current in a power supply with a PFC is affected both by the input current control (Louganski and Lai, 2007) and the voltage control, thereby making the design of a PFC control a trade-off between the mains current quality and the DC link voltage regulation (Sebastian et al., 2010).

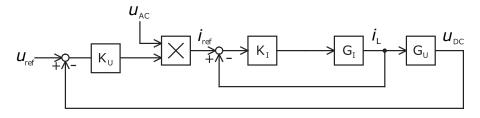

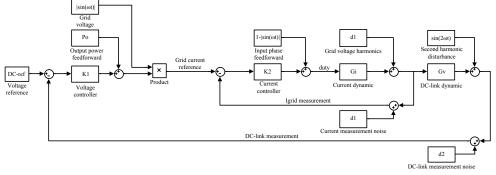

Figure 1.4. Basic cascade control structure of the PFC (Erickson and Maksimovic, 2001).

The basic control structure of the PFC is shown in Figure 1.4. The PFC controller has two main control loops; an outer voltage loop and an inner current loop (Erickson and Maksimovic, 2001). The voltage loop regulates the DC link voltage to set the reference value by setting the reference current level. The current loop then controls the current to match the current reference level set by the voltage control.

When the PFC is operating normally in the continuous current mode, the switch conduction time is varied across the mains cycle in order to force the current waveform to follow the mains voltage waveform. The most common control method is to use a PI control with current measurement for the feedback (Xie et al., 2004). Several analog and digital control integrated circuits (ICs) are available for this purpose, covering most single-phase applications. The PI controller works as long as the gain can be set high enough to ensure enough attenuation to the input voltage dynamics of the PFC, and in most cases, the current control provides sufficiently low harmonics with a high gain control only. Problems arise, however, when the gain of the feedback loop is insufficient to counter the effects of the mains voltage. Common problems caused by the mains voltage interaction are crossover distortion and a phase shift between the mains voltage and the input current (Hui Qu and Ruan, 2006). In cases where the gain cannot be sufficiently increased to provide appropriate PFC operation, feedforward and nonlinear control methods are used (Louganski and Lai, 2007).

Despite the current control, the PFC has several sources for an increase in the THD. Significant zero cross distortion arises from the oscillatory current loop response, limitations on the duty ratio, and the amount of capacitance on the DC link side of the input diode bridge (Sun, 2004). The PFC is also operating in the discontinuous current mode (DCM) when the current is less than half of

the ripple amplitude, which typically happens when the converter is operating at a less than 10-20% load (Lim and Khambadkone, 2011).

#### **1.2.5 DCM operation of the PFC**

The DCM operation occurs if the average inductor current is less than the amplitude of the switching ripple during a switching cycle. In this case, for a portion of the switching cycle there is no energy stored in the inductor and the current is clamped to zero. This results in distortions caused by a change in the control dynamics (Lim and Khambadkone, 2011), oscillations of the measured current (De Gusseme et al., 2007), and the phase lead of the current with respect to the line voltage (Sun, 2004). Numerous studies have been conducted to address distortion in the DCM operation. When a digital controller is used, the waveform can be corrected when the system goes into the DCM by calculating the average current from the sample, and a feedforward can be used to further improve the current waveform (De Gusseme et al., 2005). (Kim et al., 2017) propose a modulated carrier control to improve the current shape when the system goes into the DCM, allowing an improved power factor in low-power operation.

Even with a proper mains current shape, the DCM operation has a very limited power range owing to the high peak currents involved. A PFC is typically designed to operate in the DCM only for low power ranges of a few hundred watts. As the industrial power supply under consideration is operated with a 20–100% load corresponding to 600 W to 3 kW for most of the time, the low-power mode where the DCM operation takes place is not considered in the control design presented in this doctoral dissertation.

### **1.2.6** Current measurement

The quality of measurements is paramount to a high-performance control. In this doctoral dissertation, the timing of the measurement delay and the achievable reduction in the noise level with a proper timing of the feedback measurement signals are studied. The quality of the measurement directly affects the performance of the control design.

Figure 1.5. Current ripple measured from the output of the LTSR-15NP current transducer output. The dashed lines illustrate the sample instants at the middle of the ripple waveform.

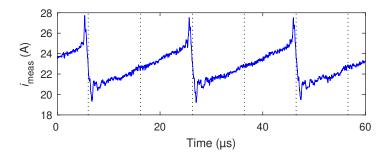

A well-known method for primary inductor current sampling is to time the sample at the middle of the switched current ripple waveform (Persson, 2001). A properly timed measurement offers a minimized delay, immunity against switching noise, and direct measurement of the average current value from the switched current waveform. The problem with this method is that the accuracy of the measurement is tied to the accurate timing of the sampling instant. When fast current slopes are sampled, even small errors in the timing will significantly impair the measurement. The problem is illustrated with a measured current shown in Figure 1.5, which depicts the current waveform at the peak of full load current.

The current ripple is typically designed to be 10-20% of the maximum peak load current (Brown, 2001). The current ripple is a compromise between the size of the inductor and the ripple amplitude with the given switching frequency and DC link voltage. The presence of the current ripple means that small deviations from the middle of the current waveform will significantly impair the measurement accuracy. For example, the highest applied pulse width produces a voltage pulse of 500 ns, during which the full 5 A ripple occurs. Thus, even a deviation of 100 ns from the center of the voltage pulse will produce an error of an ampere. In the experimental inverter, the gate driver has a 60 ns delay and the switch delays are 35 ns, both of which vary depending on temperature. Switching delays can thus significantly degrade the accuracy of the average of the current when the load current is less than nominal.

The problem with the accuracy required for the timing is further exacerbated by the fact that different switches have widely varying delays that depend on the switched current, temperature, DC link voltage, and gate driver (Brown et al., 2012). Therefore, the delay is not constant in different operating environments. Lastly, the sample and hold amplifier of the AD converter has a finite acquisition time. For example, the 12 bit AD converter MAX11115 used in this study has an acquisition time of 52 ns (Maxim Integrated, 2013), which represents 10% of the minimum pulse duration.

One option for counteracting the effect of high current slopes is to sample only a part of the current waveform with a lower slew rate (Van de Sype et al., 2004). However, this method sacrifices the improvement in the control performance achieved by the dual sampling of the current. The switched current measurement could also be filtered, but because of the large current ripple, significant filtering will add a high phase shift to the measurement, which again limits the attainable control performance (Ma et al., 2018).

All of the problems related to sample timing are the more pronounced, the more the switching frequencies are increased. With the adoption of wide band gap devices, the designer has a strong motive for increasing the switching frequencies as the output filter components are likely the heaviest and costliest part of the inverter (Gurpinar and Castellazzi, 2016; She et al., 2017) and with higher switching frequencies, the passive filter components can be sized smaller (Roy et al., 2018; Ghosh et al., 2018).

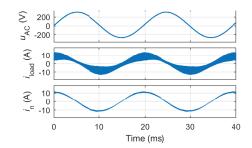

In **Publication III**, the problem with synchronous sampling is solved by using an AA filter with a bandwidth higher than the switching frequency, and the sample is timed to the low-pass-filtered version of the current.

## **1.3** Digital hardware in power electronics

In most industrial power supplies, digital hardware is required for communications, sending out the system state and alerts, and receiving commands from higher-level controls (Tötterman and Grigore, 2012). It is possible to increase the system integration by incorporating the low-level power electronics feedback control into the same digital hardware. This also provides an opportunity to use control signals and measurements for condition monitoring (Hannonen et al., 2016b), hardware-level aging detection (Hannonen et al., 2014), and component value detection (Hannonen et al., 2016a). The options available for the digital control of power electronics include the use of a microcontroller, a microcontroller along with a programmable logic, and fully customized hardware (Bielewicz et al., 1996).

A dedicated controller with sufficient peripherals for the digital power control application can also be used. This means that for a centralized power supply control, the controller is chosen so that it has sufficient hardware resources, such as pulse width modulation, and AD channels available. Although this method may be the most cost-effective one, it is also the most susceptible to single sourcing problems and the least portable among the different digital control hardware.

A common method to apply customized hardware is to use a processor for the signal processing and control functions and an FPGA for the peripheral drivers. This allows complex timing functions to be precisely executed with the FPGA hardware and general software to be used for the application. The processor can then be chosen based on the processing needs, and the required IO functionalities can be built on the FPGA. Depending on the amount of custom hardware used, this method allows hardware abstraction, and the application software can thus be written at a more general level, making the software more portable between different processors.

The benefit of custom hardware is the absence of any extra processing headroom associated with context switches, branching code execution, or instruction and pipeline delays typically present with microprocessors. With custom hardware, all of the components built inside the logic fabric run in parallel and have a minimal effect on other parts of the system. The significance of this is that the speed of the control loop is not limited by the overhead caused by other functions that would use processor time. The downside of custom hardware is the cost of development compared with software.

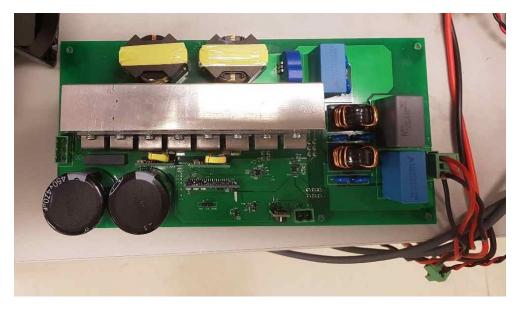

In **Publication IV**, the digital control platform and the benefits of custom hardware and a dedicated microcontroller are discussed. An example design with an FPGA and a microcontroller is presented, and it is used to control an AC/DC single-phase power supply.

Figure 1.6. XynergyXS board used to control the AC/DC power supply.

### **1.3.1** Digital control platforms used in the study

In **Publications I**, **II** and **IV**, the experimental device is a 3 kW AC/DC power supply, which is controlled by using a microcontroller for the signal processing and an FPGA for the timing of the sampling for measurements and modulation.

The power-factor-controlled power supply has a control platform that has a Cortex-M4f407 floating point microcontroller and a Xilinx Spartan 6 FPGA shown in Figure 1.6. The combination of an FPGA and a microcontroller has the benefits of easy software implementation of the control and flexibility for the peripherals that the FPGA allows.

The AC/DC power supply has a centralized digital control platform, which controls the PFC and the isolating DC/DC converter, placed on the isolated secondary side of the DC/DC converter. This is done as the PFC and DC/DC converter currents are measured using current transformers, which intrinsically provide the required galvanic isolation. Thus, the required signal crossings across the isolation barrier are limited to the AC voltage and DC link voltage measurements, neither of which requires a high bandwidth. The low bandwidth requirement for the PFC voltage measurements greatly simplifies the measurements as they can be sampled with a lower frequency, and median filtering and averaging can then be used to minimize the noise present in the measurements.

The inverter used in **Publication III** is controlled with a custom hardware implemented in an FPGA. The digital control platforms are shown in Figure 1.7. The developed FPGA control hardware platform includes analog multiplex-

Figure 1.7. Cyclone 10 LP FPGA card used for the inverter control. The designed control card includes two 2 MHz sampling analog-to-digital converters and analog multiplexers for a total of 14 AD channels in a 2x7 configuration.

ers and analog-to-digital (AD) converters. In order to minimize the latency of the calculation, the inverter control is implemented directly in the FPGA logic and written by using a hardware description language. The main benefit of the control design with custom hardware is the control calculation latency. For example, the PFC control of the AC/DC power supply takes up to 16% of the clock cycles of the interrupt routine, which is about 3  $\mu$ s with the 50 kHz control frequency and the 168 MHz DSP clock. Conversely, the total latency between a completed AD sample and a PWM register update in the FPGA controlled inverter is less than 100 ns, even though the complexities of the control algorithms are about the same.

## **1.4** Scope and motivation of the work

The research of this doctoral dissertation started in collaboration with Powernet Oy. The study aimed at making use of the benefits of a centralized digital control platform in an off-line industrial power supply. The objective of the study was to develop the health monitoring and aging detection of a power supply by utilizing the benefits of digital control design. The health monitoring algorithms were developed together with the control design as both used the same measurements and partially shared the required signal processing. A PFC converter is part of most mains-connected systems, and therefore, significant improvements in the PFC performance are beneficial to most systems.

The motivation for improving the performance of the power factor correction

(PFC) and measurements came from the need to improve the performance of an AC/DC power supply. With standard cascaded PI control loops, neither the current nor the voltage loop performs satisfactorily. There are multiple reasons why the performance was not sufficient without special control methods. In the case of the current control, the digital control of the individual boost circuits of the parallel boost converter was not deemed to be reasonable. The power supply was controlled with a 50 kHz control frequency and with both boost converters having the same duty cycle command. This limited the attainable gain of the current loop, and therefore, the control loop control had to be designed with a line voltage feedforward. The Lyapunov method was used as the resulting control is directly derived from the structure and dynamics of the power supply.

The performance limitation of the voltage control is a fundamental property of a single-phase PFC. Because the input current is sinusoidal, the resulting sinusoidal ripple in the DC link is unavoidable. The performance of the DC link voltage during a load step cannot be achieved with a linear controller without sacrificing the input current THD.

In order to achieve satisfactory dynamics for the single-phase inverter, a high control bandwidth is required, which is obtainable with dual sampling of the measurements. The dual sampling is used to get average current and voltage measurements from the switched current waveform. Without the slew rate limitation obtainable by the anti-alias (AA) filtering, switching noise cannot be avoided. Furthermore, the narrowest switched pulse is only 500 ns, and with all of the uncertainties present in the generated voltage pulses, sampling at the middle point of the voltage pulse is not consistent enough to be practical. The inverter sampling was implemented by dual sampling of the filtered current. The filter was designed to have a cutoff frequency that is higher than the modulation frequency, and the sampling instant was then timed to provide over 20 dB of improvement of the measurement noise.

#### **1.4.1** Digital control platform

In **Publication IV**, the choice between an off-the-shelf microcontroller, a half customizable embedded system with a microcontroller and an FPGA, and a fully customizable embedded system implemented in the FPGA is discussed

in the context of a digital control platform. The publication addresses the use of a centralized digital control platform for the control of the PFC and the DC/DC converter. The digital platform is also used for condition monitoring purposes, which is the topic of several publications and the doctoral dissertation of Dr. Janne Hannonen.

### **1.4.2** Improvements in the current control

A common way to improve the linear current loop performance is to include feedforward terms in the control. For example, an input voltage feedforward has been used either directly (Xie et al., 2004) or by modeling the admittance and then using the inverse of the admittance model to filter the mains voltage in order to produce the feedforward (Louganski and Lai, 2007).

A nonlinear control can be designed either with a sliding mode control or with Lyapunov-based methods in both the continuous and discrete time domains. The nonlinear control law has been designed by using Sontag's optimal control with a continuous (Pahlevaninezhad et al., 2012) and a discrete control design (Das et al., 2013). A digital version of the sliding mode control was proposed in (Marcos-Pastor et al., 2016). In all the current loop control designs, the objective is to make the measured current closely follow the reference current waveform, which can then act as a control variable of the voltage loop. The nonlinear control methods commonly require division and square root operations, which tend to be much more computationally intensive than linear control methods.

In **Publication I**, the line voltage feedforward term is formed by using the Lyapunov function. The Lyapunov-function-based control design comprises a stabilizing control law along with the Lyapunov function, which can be used to prove the stability. The control law is a PI controller with a mains voltage feedforward term, which arises from the dynamic equation of the boost converter. The control is applied by using a digital controller and calculated by using only sum and multiplication functions.

With the standard cascade PI control, the crossover has an oscillatory response, which stems from an inadequate current loop gain (Louganski and Lai, 2007). The system is controlled by using an integrating control design, and the result is a common PI controller with an input voltage feedforward term. The online implementation is simplified by omitting a division operation without affecting the current reference tracking performance. With the designed control, the crossover spike is completely removed from the input current waveform.

#### **1.4.3** Improvements in the voltage control

The DC link performance is significantly affected by the requirements for the mains current distortion. The key issue is the rectified current adding a twice the mains frequency component to the DC link voltage. The ripple voltage is introduced to the current reference through the current control. Thus, the higher the gain of the voltage control is at the second harmonic of the mains frequency, the higher is the current distortion (Sebastian et al., 2010). The options to reduce the current-distorting effect of the DC link ripple are either to filter the ripple or design a nonlinear control and a controlled parameter to control the DC link indirectly, thereby reducing the effect of the ripple.

A ripple cancellation method where the ripple is estimated and the estimate is then subtracted from the measurement was introduced in (Leung et al., 2016b) and (Leung et al., 2016a). The estimation and cancellation were accomplished with a dedicated analog circuitry, and it was shown that the bandwidth of the DC link control can be increased. A similar estimation with digital signal processing was presented in (Chiang et al., 2016), where the authors used a phase-locked loop to accurately estimate the ripple. In both of these cases, the achieved performance is regulation of the DC link in about two mains cycles.

Nonlinear control solutions based on Lyapunov functions have also been proposed. In (Li and Zhong, 2014), the voltage control was designed with a measurement from peak load power, which was used to define a feedforward term to improve the voltage control loop regulation. The control loop was designed by using a discrete form of the Lyapunov equation. Another design with also a discrete nonlinear control was proposed in (Das et al., 2013). The controller is a nonlinear state-space controller, which controls both the current and the voltage. The performance of both controllers defined with a discrete form of the Lyapunov function is very similar and stabilizes the DC link in two to three mains cycles.

A fuzzy logic controller in the regulation of the DC link was studied in (Faucher et al., 2009). The use of fuzzy logic is a way to model human thinking by following a thought process like "if the error is large, and the rate of change for the error is negative and small, then a slight adjustment is needed." This thought process is modeled by fuzzy rules, which are then defuzzified to produce a control signal. The fuzzy logic controller uses measurements from the DC link and the derivative of the error between the set value and the measurement. The controller uses the Takagi–Sugeno (T-S) fuzzy logic controller is comparable with Lyapunov-based controllers, with the system achieving regulation within three mains cycles.

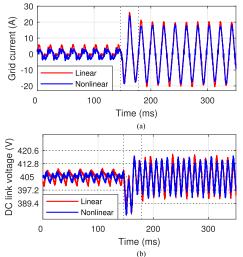

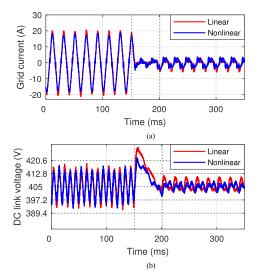

In **Publication II**, the DC link control is designed by using a Takagi–Sugenostyle fuzzy control called a parallel distributed control (PDC). The controller is a nonlinear PI controller with the gain scheduled with the DC link voltage. The difference between the PDC control and the fuzzy logic control is that the PDC is based on a mathematical model of the system and can be analyzed using nonlinear control methods. When the traditional PI voltage loop offers a compromise between transient speed and steady-state harmonics, the developed fuzzy controller effectively decouples the transient and steady-state control performances making it possible to extend the transient speed without excessively distorting the input current. The PDC is cheap in terms of the required calculation effort and offers excellent static performance for both the DC link and input current when compared with a similarly tuned linear controller. The designed controller also stabilizes after a load step within three mains cycles, which matches or surpasses the performance attained with more complex nonlinear designs.

### **1.4.4** Dual sampling inverter control measurements

The performance of a control loop is significantly affected by the speed and accuracy of the measurements. In **Publication III**, custom hardware is designed to offer high-accuracy current measurement in a dual sampled single-phase inverter. The custom hardware is designed to provide minimal latency between the sampled measurement and the control update. The benefit of the optimized measurement is that the current measurement band can be significantly increased compared with a situation where the same ripple attenua-

# **1.5 Research methods and scientific contributions of the doctoral dissertation**

tion is achieved with anti-aliasing filtering only. The current measurement bandwidth is maximized by using an AA filter with a bandwidth wider than the switching frequency, which does not significantly attenuate the switching ripple, yet decreases the slew rate of the sampled signal. The lower rate of change makes it possible to take accurate samples at a double switching frequency rate even at very high duty cycles.

## **1.5 Research methods and scientific contributions of the doctoral dissertation**

All of the studies and the reported improvements in performance were verified in the laboratory by using experimental devices. The study applies system modeling and signal processing for the online measurements and the off-line data analysis and processing.

The key scientific contributions of this doctoral dissertation are

- Design of the PFC current control feedforward with Lyapunov's stability theorem

- Development of a nonlinear algorithm to reduce the harmonics and improve the speed of convergence in a single-phase PFC converter

- Design of improved current measurement in a high di/dt current waveform

## **1.6** Structure of the doctoral dissertation

The rest of the doctoral dissertation concentrates on utilizing the benefits of the digital control system, with the focus of the control design on the power factor correction. Chapter 2 introduces the power factor control hardware used in the study. Further, the chapter outlines the operation of the boost power factor control and the issues in the control of the DC link. The chapter addresses the choice that has to be made between the low steady-state current harmonics and the fast transient performance of the control design. Moreover, the chapter discusses the use of fuzzy control for the DC link control and how it can be effectively used to improve the steady-state current waveforms when high gains are used in the DC link control.

The current control design is also analyzed by using the Lyapunov function. The use of a very simple feedforward to improve the performance of the current control is discussed, and it is shown to be derived from the direct use of the Lyapunov theory.

Chapter 3 focuses on the effect of the measurement timing and the method to mitigate the effects of high current slew rates and component delays. The accuracy of the measurement is important as the attainable performance is limited by the quality of the measurements used for the feedback.

Chapter 4 concludes the doctoral dissertation and discusses future research.

# 2 PFC control design

The performance of a PI-controlled PFC depends on achieving a high enough gain to provide distortion-free current reference tracking. Because the PFC can only feed power in one direction, the power supply is not controllable at the mains voltage zero cross instant, and the recovery from the mains zero crossing will add to the distortion if the response is too oscillatory. The achieved control gain might be too low because of a low switching frequency to mains frequency ratio or excessive noise present in the measurements.

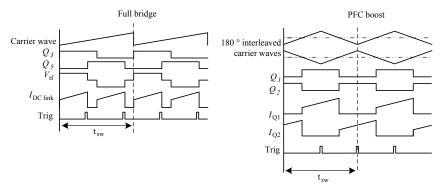

In this case, the control frequency is limited and both of the boost switches are controlled with the same duty cycle. As reported in (Hannonen et al., 2016b), the control of the AC/DC power supply takes up to 69% of the processing resources when the control is run at 50 kHz, and therefore, only one controller is used to save resources. Furthermore, a design without an individual PFC control saves significant calculation resources as all of the power supply controls can be run on the same interrupt. This reduces the overhead when compared with a system with several interrupt service routines. The control is also run at a frequency lower than the switching frequency as opposed to a control with at every switching cycle, which would imply the control being run at 200 kHz.

The control is calculated at a rate of 50 kHz, and only the largest of the two measured currents are used for the feedback. Because the two boost converters are controlled with the same duty cycle, there is invariably a difference between the two measured currents, as the hardware is not exactly identical. The use of only the higher of the two currents was deemed the simplest option as the one calculated current controller then limits both currents without extra logic. On the downside, this also adds disturbance to the measurement, which is then amplified by the control.

# 2.1 Power factor control hardware used in the study

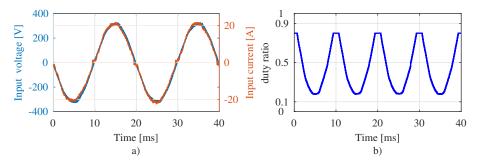

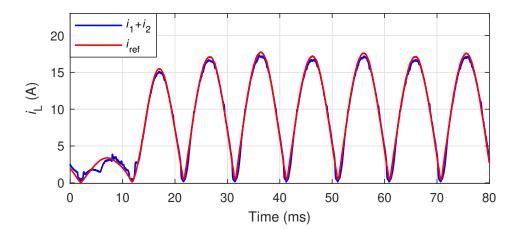

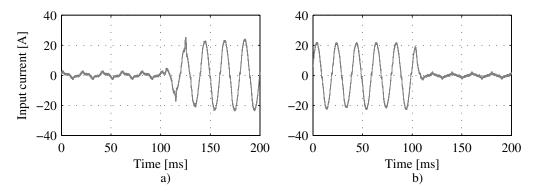

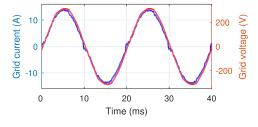

The objective of the entire PFC system is to shape the grid current to follow the grid voltage waveform and to keep the DC link voltage at 405 V. The PFC operation is accomplished by measuring the DC link voltage, the mains current, and the mains voltage, after which a feedback is used for forcing the PFC current to track the mains voltage. The DC link voltage is thus controlled by changing the level of the peak of the mains current to such a value that the charging and discharging currents are balanced.

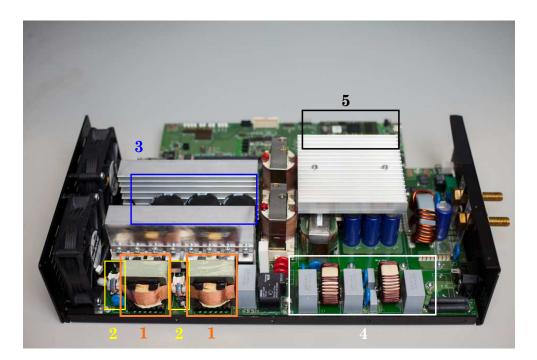

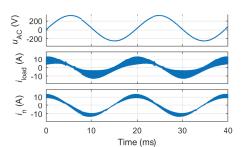

The PFC hardware used to study condition monitoring and power factor correction has two interleaved boost converters for the PFC operation and an isolating DC/DC power supply for voltage level translation and galvanic isolation. The use of two boost converters in parallel helps in distributing losses and allows the use of smaller individual inductors. The parallel operation makes it possible to drive the boost converters in opposite phases, which significantly reduces the grid current ripple and thus simplifies further power line filtering. The power supply is presented in Figure 2.1 with the main components highlighted.

The control system measures the mains voltage  $u_{AC}$ , the DC link voltage  $u_{DC}$ , and the switch currents  $i_1$  and  $i_2$ . The switch currents are measured using current transformers. In order to guarantee that the transformers are not saturated, the maximum duty cycle for the switch is limited to 0.8. This ensures that the designed circuit does not go into saturation, but duty cycle limitation also introduces a distortion at the voltage zero crossing instant as a result of insufficient volt seconds across the input inductor.

In order to save on the calculation resources available in the microcontroller, only one PI controller is used and the resulting duty cycle is used for modulation of both of the boost converters. In order to make the maximum current reference level work properly, only the larger of the measured currents is used for feedback.

The controller uses the mains voltage for current reference generation and the feedforward control of the current loop. The mains current is obtained by multiplying the output of the DC link voltage control with the measured mains

Figure 2.1. Power supply used for the experimental measurements. PFC inductors 1 and 2 are the current transformers used to measure the PFC current, 3 indicates the 1.5 mF DC link capacitors, 4 is the EMI filter, and 5 is the Xynergy embedded control platform.

voltage. The DC link voltage is used as a feedback for the voltage control.

# 2.2 Construction of the input current controller

The current control is designed first, using a Lyapunov function for construction of the current controller (**Publication I**).

The control model for the inductor current of a boost converter is

$$L\dot{i}(t) = u_{in}(t) - u_{dc}(t) \cdot d(t).$$

(2.1)

In order to increase the low-frequency performance, the system is augmented with an integral of the controlled state multiplied by an integral constant. As the integration is done by the controller, the integral gain can be freely chosen and is here denoted by  $K_I$

$$L\dot{i}(t) = u_{in}(t) - u_{dc}(t) \cdot d(t)$$

$$\dot{\omega}(t) = K_I i(t).$$

(2.2)

(2.3)

$$\dot{\boldsymbol{\omega}}(t) = K_I i(t). \tag{2.3}$$

The system (2.2)–(2.3) depends on the input voltage, the DC link voltage, and the controlled duty cycle d(t). In order to design a stabilizing control law, a Lyapunov function (V(x(t))) is constructed. The control and the stability proof are thus built in parallel. The Lyapunov function is defined as a positive definite function, i.e., a function that only gets positive values, along which the dynamical system gets only negative values (Haddad and Chellaboina, 2008). Formally

$$V(0) = 0,$$

(2.4)

$$V(x(t)) > 0,$$

(2.5)

$$V'f(x(t)) \le 0.$$

(2.6)

In order to use the Lyapunov function to construct a control law, a simple quadratic Lyapunov function is used

$$V = \frac{1}{2}i(t)^2 + \frac{1}{2}\omega(t)^2.$$

(2.7)

Substituting (2.2) and (2.3) into (2.6) yields

$$V'f(x(t)) = i(t) \cdot \dot{i} + \omega(t) \cdot \dot{\omega}(t)$$

(2.8)

$$= i(t) [u_{in}(t) - u_{dc}(t) \cdot d(t)] + K_I \omega(t) i(t).$$

(2.9)

The control law d(t) then has to be designed such that (2.9) is negative definite. One option is

$$d(t) = \frac{1}{u_{dc}(t)} \left( u_{in}(t) + K_I \omega(t) + K_p i(t) \right).$$

(2.10)

Substituting (2.10) into (2.9) gives

$$V'f(x(t)) =$$

$$i(t) \cdot \left[ u_{in}(t) - u_{dc}(t) \cdot \frac{1}{u_{dc}(t)} \left( u_{in}(t) + K_I \omega(t) + K_p i(t) \right) \right] \qquad (2.11)$$

$$+ K_I \omega(t) i(t)$$

$$=-K_p i(t)^2.$$

(2.12)

Because the Lyapunov function derivative is negative definite, the stability is guaranteed. The effect of the designed control can be seen by substituting (2.10) into the controlled system (2.2)–(2.3)

$$L\dot{i} = u_{in}(t) - u_{dc}(t) \cdot \frac{1}{u_{dc}(t)} \left( u_{in}(t) + K_I \omega(t) + K_p i(t) \right)$$

(2.13)

$$= -K_p i(t) - K_I \omega(t) \tag{2.14}$$

$$\dot{\boldsymbol{\omega}}(t) = K_I i(t). \tag{2.15}$$

As can be seen, the system dynamics is only dependent on the positive constants set by the user. The effect of the mains voltage is thus practically eliminated from the system dynamics.

### 2.2.1 Simplifying the feedback controller

Because the direct application of the Lyapunov function requires a division operation, a simpler version of the controller is designed. It is pointed out that during operation, the DC link voltage varies within 10–20% of the reference value. The dynamics of the DC link is also significantly slower than the bandwidth of the current control loop, even at large load changes. Therefore, the DC link term given in (2.10) can be considered constant without a significant error, and the control can be calculated from the mains voltage measurement with multiplication by a constant of  $\frac{1}{u_{ref}}$ , thus avoiding a division in the calcu-

lation of the control law. This simplifies the control law to

$$d(t) = \frac{1}{u_{\text{ref}}} \left( u_{\text{in}}(t) + K_I \omega + K_p i(t) \right)$$

(2.16)

$$= u_{\rm in}(t) \cdot \frac{1}{u_{\rm ref}} + \frac{K_p}{u_{\rm ref}} i(t) + \frac{K_I}{u_{\rm ref}} \omega(t).$$

(2.17)

Combining this with the integrating state in Figure 2.3 and noting that the gains  $K_p$  and  $K_i$  are freely chosen constants, the current controller is

$$d(t) = K_p i(t) + K_I \omega(t) + \frac{1}{u_{\text{ref}}} \cdot u_{\text{in}}(t)$$

(2.18)

$$\dot{\boldsymbol{\omega}}(t) = K_I i(t). \tag{2.19}$$

As the gains  $K_P$  and  $K_I$  can be chosen freely, the factor multiplying them by a constant of  $\frac{1}{u_{ref}}$  can be omitted. The resulting controller can be considered a standard PI controller with an extra feedforward term  $\frac{1}{u_{ref}} \cdot u_{in}(t)$  added for decoupling the mains voltage dynamics.

### 2.2.2 Control tuning

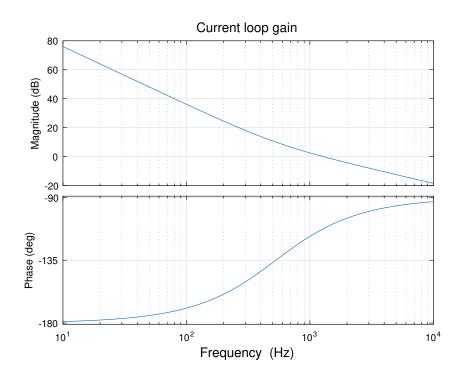

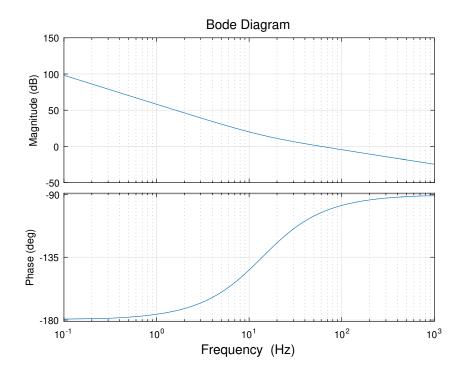

The control design of a PI control is designed by traditional methods using a Bode plot. Because only the largest of the sampled inductor currents is used for the control, the current loop dynamics is calculated applying a  $500 \,\mu\text{H}$  inductance. With the feedforward term canceling the effect of the mains voltage, the modeled system is the current equation of the input inductor with the inductor voltage as the controlled parameter

$$\dot{i}(t) = \frac{u(t)}{L}.$$

(2.20)

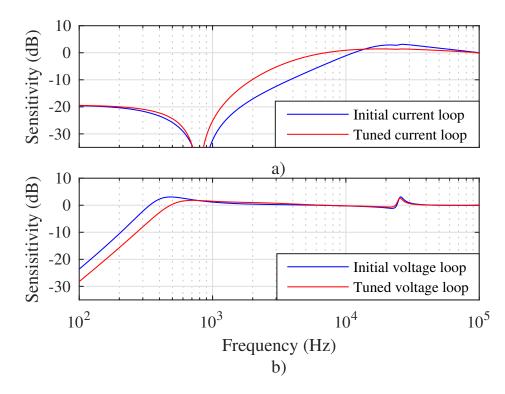

The current loop is designed to have a minimum gain of 40 dB at the mains voltage frequency and a crossover frequency of approximately 1 kHz, which provides a phase shift of less than  $0.05^{\circ}$  for the reference tracking response. The final current loop is then tuned experimentally to yield a satisfactory response. The final tuned controller loop gain is shown in Figure 2.3 with the gain given in Table 2.1. The bandwidth of the controller can be read from the 0 dB point of the loop gain function, and it can be seen to be 1.3 kHz with the phase margin of  $68^{\circ}$ . The effect of the feedforward term is presented with experimental results in Section 2.4.

# **2.2.3** Effect of the DC link voltage on the inductor current control

Because the actual DC link voltage influences the actual current in the inductor, but its effect is not mitigated entirely by the simplified control (2.18), the effect of the DC link voltage variation is estimated. Because the effect enters the control loop through the duty cycle, the effect is investigated by calculating the inductor current with an additive perturbation term  $\Delta(t)$ , which represents the ripple signal of the DC link. The response is modeled by adding the perturbation to the dc link voltage in the control model (2.1) which yields

$$L\dot{i}(t) = u_{\rm in}(t) - (u_{\rm dc}(t) + \Delta(t)) \cdot d(t)$$

(2.21)

$$\Leftrightarrow u_{\rm in}(t) - u_{\rm dc}(t) \cdot d(t) - \Delta(t) \cdot d(t)$$

(2.22)

As the disturbance is modeled as an additional input, the disturbance response can be calculated from the closed loop equation by adding the disturbance to the closed loop equation (2.13) - (2.15). The duty cycle d(t) gets values between 0 and 1, the worst-case effect of the disturbance is obtained when d(t) = 1. Using the worst case amplitude for the disturbance yields

$$L\dot{i}(t) = -K_p i(t) - K_I \omega(t) - \Delta(t)$$

(2.23)

$$\dot{\boldsymbol{\omega}}(t) = K_I i(t). \tag{2.24}$$

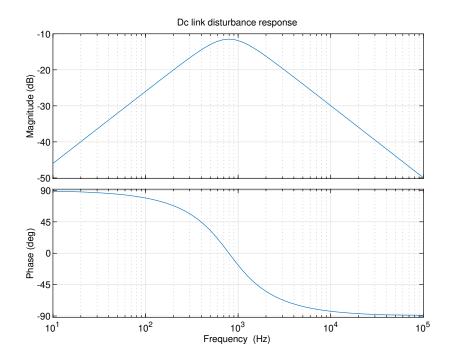

The effect of the DC link voltage disturbance on the inductor current can be evaluated by calculating the response from  $\Delta(t)$  to inductor current i(t)which is seen in Figure 2.2. It should be noted that with the simplification of omitting the division in the control algorithm, the effect of the DC link is not mitigated. However, with the nominal 400V DC link voltage and during normal operation, the voltage varies between 390 and 410 V at double the mains frequency, and thus the disturbance has an amplitude of less than 10 % of the modulation range. This effect is further attenuated by more than -20 dB by the control as seen in the disturbance sensitivity function response shown in Figure 2.2, and therefore, the DC link voltage ripple has a limited effect on the control performance.

Figure 2.2. Effect of the DC link disturbance on the inductor current.

Table 2.1. Converter current control parameters

| Symbol         | Quantity                      | Value   |

|----------------|-------------------------------|---------|

| L              | boost inductor                | 500 µH  |

| С              | DC link capacitance           | 1500 µF |

| $K_{\rm P_1}$  | proportional gain             | 3.7500  |

| $K_{I_1}$      | integrator gain               | 12500   |

| $f_{\rm ctrl}$ | control calculation frequency | 50 kHz  |

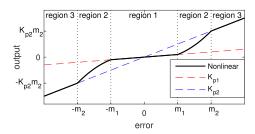

# 2.3 Nonlinear DC link voltage control

The voltage control is designed next, using a Takagi–Sugeno controller for construction of the voltage controller (**Publication II**). The DC link control

Figure 2.3. Loop gain of the PFC current loop.

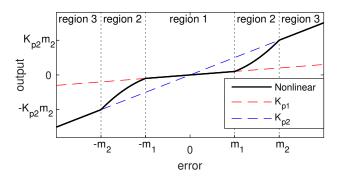

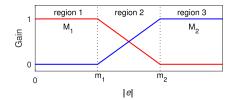

Figure 2.4. Nonlinear voltage control gain is a weighted sum of the two PI controllers. The widths of the regions are chosen so that the maximum load ripple amplitude is within the linear region.

balances the input and output currents so that the average value of the DC link is kept constant. The bandwidth of the control has to be high enough to ensure that at the moment of the full load step, the DC link voltage will not drop so low that either the DC/DC converter or the PFC current control will lose its ability to control the voltage. The speed of the load step is determined by the bandwidth, or correspondingly, the gain of the DC link control. As discussed in (Sebastian et al., 2009), the higher gain also results in higher harmonics of the input current.

In order to increase the convergence speed, the influence of the DC link ripple has to be mitigated. This increases the distortion caused by the voltage loop, and therefore, an improved control is designed in such a way that low gains are used for the DC link ripple, but the gain is increased as the error increases when a higher control effort is needed. This type of control can be designed by using a fuzzy control.

Fuzzy models of Takagi–Sugeno (T-S) style can be used to define nonlinear models by using several linear models and weighting functions called fuzzy membership functions. A T-S model-based control has thus several state-space control gains, which are combined together with a fuzzy logic. A T-S-type nonlinear control allows mathematical analysis with matrix inequalities, and it can be used with the robust and optimal control theory (Tanaka and Wang, 2004).

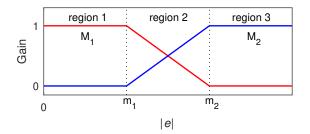

The basic idea behind the fuzzy control is illustrated in Figure 2.4, which shows the composite gain function. The gain function is designed to have three regions. In region 1, the gain is constant and the gain function is linear in terms of error. The constant, linear gains limit the amount of additional distortion from the nonlinearity of the controller. In region 3, the gain is also linear with a high gain, and region 2 has gains that are an average of the low and high gains. In this way, the high gain control is used when the error is large, but low gains are used to provide a low distortion, and there is a transition region where the gain changes with the size of the error. The membership functions with which the gains are weighted are shown in Figure 2.5. Mathematically, these functions are

$$M_1 = \frac{m_2 - e(t)}{m_2 - m_1}, \quad M_2 = \frac{e(t) - m_1}{m_2 - m_1}$$

(2.25)

$$K_1 = [K_{P_1}, K_{I_1}], \quad K_2 = [K_{P_2}, K_{I_2}],$$

(2.26)

where  $K_1$  and  $K_2$  are the gain vectors for the high- and low-gain PI controllers. The controller then uses the two PI controllers and weighs their gains with the

Figure 2.5. Membership functions for fuzzy systems.

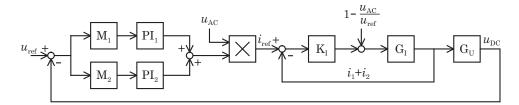

Figure 2.6. Final PFC control with the designed current and voltage control.

membership functions (2.25) to provide the appropriate control action. The block diagram of the fuzzy controller is shown in Figure 2.6. A control of this type is called a parallel distributed compensator (PDC) (Wang et al., 1995), and it is written as

$$u = \sum_{i=1}^{r} M_i K_i x(t), \quad i = 1, 2, 3...r.$$

(2.27)

The PDC allows a systematic state feedback control design to be made directly from the T-S fuzzy model and also offers a framework for analyzing the stability of the control design.

## 2.3.1 DC link control design

The control model for the DC link capacitor voltage is designed with the input current i(t) as a controlled variable. The modeled plant is thus

$$C \cdot \dot{u}_{\mathrm{DC}}(t) = i(t) - \frac{u_{\mathrm{DC}}(t)}{R}, \qquad (2.28)$$

where  $u_{DC}(t)$  is the controlled DC link voltage, C is the DC link capacitance, i(t) is the controlled current, and R models the load as a resistance. As the

control objective is to regulate the error between the measured DC link voltage and the reference to zero, the system is represented with the controlled state being the error between the DC link voltage  $u_{DC}(t)$  and the reference  $u_{ref}$

$$e(t) = u_{\rm DC}(t) - u_{\rm ref}.$$

(2.29)

With the change of coordinates, the controlled plant is

$$\dot{e}(t) = \frac{1}{C} \cdot \left( i(t) - \frac{e(t)}{R} \right). \tag{2.30}$$

As with the current control, the plant is augmented with an integrating state to guarantee a zero steady-state error. Adding an integrator state  $\dot{\omega}(t)$  gives

$$u(t) = -K_P e(t) + \omega(t) \tag{2.31}$$

$$\begin{aligned} u(t) &= -K_P e(t) + \omega(t) \end{aligned} \tag{2.31} \\ \dot{\omega}(t) &= -K_I e(t). \end{aligned}$$

Combining (2.30) and (2.31)–(2.32) gives the state-space model of the capacitor voltage controlled with an integrating controller

$$\dot{e}(t) = e(t) \cdot \left(-\frac{K_P}{C} - \frac{1}{RC}\right) + \frac{1}{C}\omega(t)$$

(2.33)

$$\dot{\boldsymbol{\omega}}(t) = -K_I \boldsymbol{e}(t). \tag{2.34}$$

To control the system (2.33)–(2.34) with the PDC controller (2.27), the PI controller (2.31)–(2.32) is replaced by

$$u(t) = e(t) \cdot (M_1 K_{P_1} + M_2 K_{P_2}) + \omega(t)$$

(2.35)

$\dot{\omega}(t) = e(t) \cdot (M_1 K_{P_1} + M_2 K_{P_2}) + \omega(t)$

(2.36)

$$\dot{\omega}(t) = e(t) \cdot (M_1 K_{\mathrm{I}_1} + M_2 K_{\mathrm{I}_2}).$$

(2.36)

The membership functions  $M_1$  and  $M_2$  determine the control behavior so that when the error is less than  $m_1$  or more than  $m_2$ , only a single PI controller is used. Therefore, the controller implementation differs from the traditional PI control only in region 2, where the gains are interpolated.

For implementation, the controller (2.35)–(2.36) is converted into a simpler form. As stated above, in the case of the PI-controlled DC link voltage, the measured signal z(t) is the absolute value of the error |e(t)| between the measured DC link voltage and the reference, and  $m_i$  are the voltage levels used to schedule the gains of the controllers. Substituting (2.25) into (2.35)–(2.36) yields

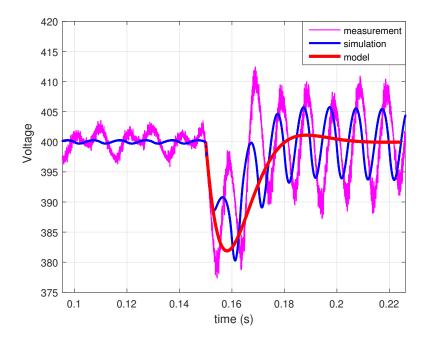

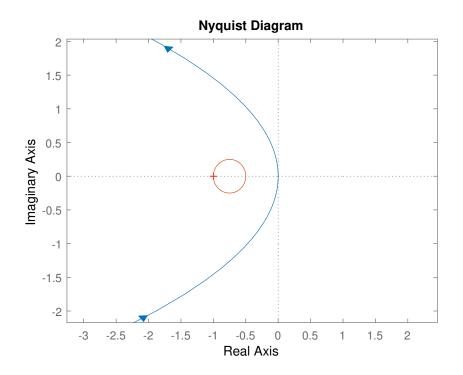

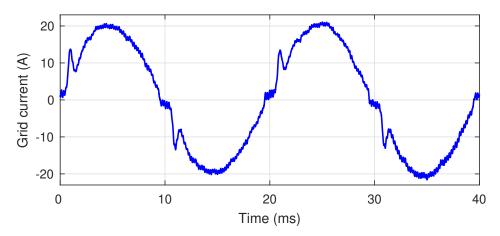

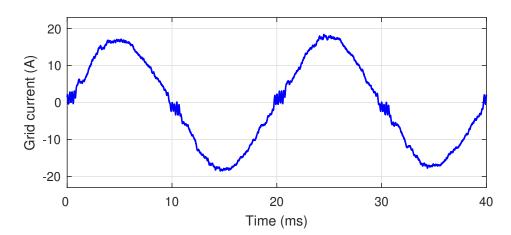

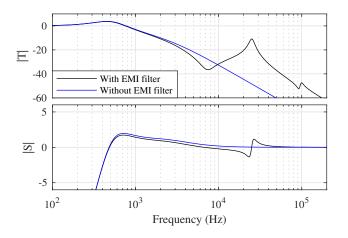

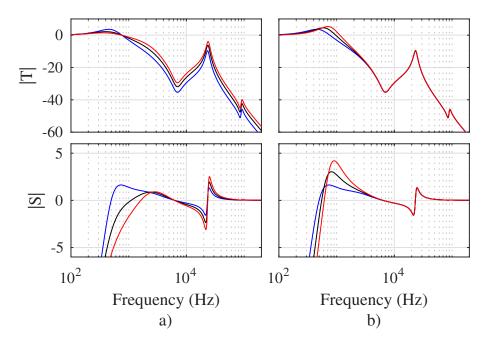

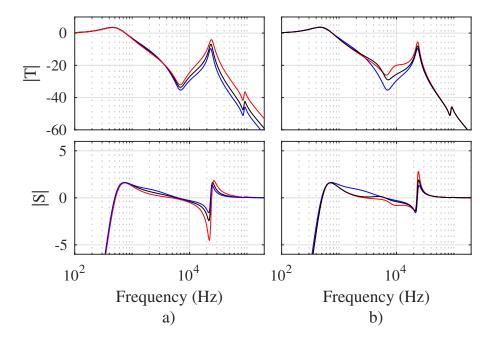

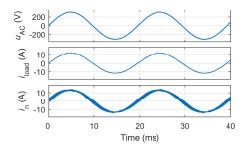

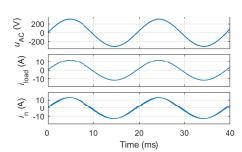

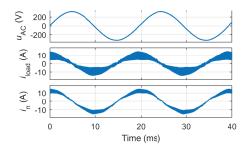

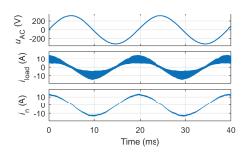

$$u(t) = e(t) \cdot \left( (m_2 - |e(t)|) \frac{K_{P_1}}{m_2 - m_1} + (|e(t)| - m_1) \frac{K_{P_2}}{m_2 - m_1} \right) + \omega(t)$$