Lappeenranta-Lahti University of Technology LUT School of Engineering Science Computational Engineering and Technical Physics Technical Physics

## Tarusisko Hirvenoja

# SILICON PIN-DIODES WITH GATE INDUCED PASSIVATION - FABRICATION AND CHARACTERISATION

Master's Thesis

Examiners: Prof. Panja Luukka

M. Sc. (Tech.) Markku Kainlauri

Supervisors: M. Sc. (Tech.) Markku Kainlauri

**ABSTRACT**

Lappeenranta-Lahti University of Technology LUT

School of Engineering Science

Computational Engineering and Technical Physics

**Technical Physics**

Tarusisko Hirvenoja

SILICON PIN-DIODES WITH GATE INDUCED PASSIVATION - FABRICATION

AND CHARACTERISATION

Master's Thesis

2021

72 pages, 45 figures, 11 tables.

Examiners:

Prof. Panja Luukka

M. Sc. (Tech.) Markku Kainlauri

Keywords: silicon PIN diode detector, induced junction, Al<sub>2</sub>O<sub>3</sub> passivation

Silicon PIN diode has been common and efficient configuration for detector purposes for long time. In order to reduce the dead layer on top of the detector, PIN diodes with induced passivation were fabricated and characterised. The induced junction was created on n-type high resistivity silicon by taking advantage of field effect passivation achieved with charged oxide, Al<sub>2</sub>O<sub>3</sub> in this case. Gates were fabricated on top of the diodes to control the charge on the silicon surface. Two transparent gate materials were tested: graphene and indium tin oxide (ITO). The gated diodes were compared to other types of diodes fabricated on the same wafers. The diodes were characterised with four measurement techniques: current-voltage (IV), capacitance-voltage (CV), transient current technique (TCT) and radiation measurements. In IV measurement it was demonstrated that it is possible to change the state in the diode with gate biasing. The leakage current level was few  $nA cm^{-2}$  and the detectors showed response to visible light and gamma radiation.

## TIIVISTELMÄ

Lappeenrannan-Lahden teknillinen yliopisto LUT School of Engineering Science Laskennallinen tekniikka ja teknillinen fysiikka Teknillinen fysiikka

Tarusisko Hirvenoja

## PII PIN-DIODIT HILAINDUSOIDULLA PASSIVOINNILLA - VALMISTUS JA KARAKTERISOINTI

Diplomityö

2021

72 sivua, 45 kuvaa, 11 taulukkoa.

Tarkastajat: Prof. Panja Luukka

DI Markku Kainlauri

Hakusanat: pii PIN diodi ilmaisin, indusoitu liitos, Al<sub>2</sub>O<sub>3</sub> passivointi

Pii PIN diodi on ollut yleinen ja tehokas rakenne ilmaisinsovelluksissa jo pitkän aikaa. Ilmaisimen pinnalla olevan kuolleen kerroksen ohentamiseksi valmistettiin ja karakterisoituun PIN diodeja indusoidulla passivoinnilla. Indusoitu liitos valmistettiin n-tyypin korkean resistiivisyyden piille hyödyntäen varautuneen oksidin, tässä tapauksessa  $Al_2O_3$ :n, aiheuttamaa kenttäpassivointia. Diodien päälle valmistettiin hilat, joilla oksidin varausta voidaan säädellä. Kahta läpinäkyvää hilamateriaalia testattiin: grafeenia ja indiumtinaoksidia (ITO). Hilallisia diodeja verrattiin muihin diodityyppeihin samoilla kiekoilla. Diodeja karakterisoitiin neljällä eri mittaustekniikalla: virta-jännite (IV), kapasitanssi-jännite (CV), muutostilan virtaa mittaavalla menetelmällä (TCT) ja säteilymittauksilla. IV mittauksilla osoitettiin, että diodin tilaa on mahdollista muuttaa syöttämällä jännitettä hilaan. Vuotovirran taso oli muutamia  $nA\ cm^{-2}$  ja ilmaisimet osoittivat vastetta näkyvälle valolle ja gammasäteilylle.

**PREFACE**

The work for this Master's Thesis was mainly conducted at VTT Technology Research

Centre of Finland (VTT) in micro- and nanotechnology research center Micronova. The

work was funded from Business Finland project RaPtor.

First I would like to thank my supervisor Markku Kainlauri for all his guidance throughout

the entire process. Our frequent discussions made it easier for me to stay on top of the

work. I also thank my examiner, Panja Luukka, for her expertise on the field and getting

me a contact to Helsinki Institute of Physics Detector Laboratory to do measurements.

I would like to thank Olli-Pekka Kilpi for the work he did for the fabrication and all the

help and encouragement during the process. I'm thankful to Miika Soikkeli for his help

and patience during the gate processing, especially on the graphene transfer. I would

also like to thank Shudhasil Bhartuar, Erik Brücken and the helpful staff of HIP Detector

Laboratory for doing the CV, TCT and radiation measurements and letting me to come

observe.

I'm also grateful for our research team leader Sanna Arpiainen taking me into her team

and giving me a chance to work on this project. All our team members and other trainees

have been important part of my experience at VTT.

These years in LUT have passed so much faster than I expected. Our guild, Lateksii, and

all the people who are part of it were important part of my experience. I hope that our

paths will cross also in the future.

At the end, I'd like to thank my closest friends for being there to listen to all my complaints

but also for all the good times we have had. I'm also thankful for my parents raising me

to have the confidence to get through whatever I want to.

Espoo, October 4, 2021

Tarusisko Hirvenoja

## **CONTENTS**

| LI              | ST O         | OF ABBREVIATIONS                  | delimitations 9 e thesis 11  CONDUCTOR DETECTORS 12 materials 12 adiation detector 16 on 17 ene 20 n tin oxide (ITO) 21  FION 22 raphy 22 raphy 22 reversal 23 ene transfer 25 ene gate 31 ene gate 31 fERISATION 37 ge (IV) 37 |  |  |  |  |

|-----------------|--------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LIST OF SYMBOLS |              |                                   |                                                                                                                                                                                                                                 |  |  |  |  |

| 1               | INTRODUCTION |                                   |                                                                                                                                                                                                                                 |  |  |  |  |

|                 | 1.1          | Background                        | g                                                                                                                                                                                                                               |  |  |  |  |

|                 | 1.2          | Objectives and delimitations      | ç                                                                                                                                                                                                                               |  |  |  |  |

|                 | 1.3          | Structure of the thesis           | 11                                                                                                                                                                                                                              |  |  |  |  |

| 2               | BAS          | SICS OF SEMICONDUCTOR DETECTORS   | 12                                                                                                                                                                                                                              |  |  |  |  |

|                 | 2.1          | Semiconductor materials           | 12                                                                                                                                                                                                                              |  |  |  |  |

|                 | 2.2          | PN-junction                       | 14                                                                                                                                                                                                                              |  |  |  |  |

|                 | 2.3          | PIN diode as radiation detector   | 16                                                                                                                                                                                                                              |  |  |  |  |

|                 | 2.4          | Induced junction                  | 17                                                                                                                                                                                                                              |  |  |  |  |

|                 | 2.5          | Gated diode                       | 19                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 2.5.1 Graphene                    | 20                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 2.5.2 Indium tin oxide (ITO)      | 21                                                                                                                                                                                                                              |  |  |  |  |

| 3               | DIO          | DIODE FABRICATION 2               |                                                                                                                                                                                                                                 |  |  |  |  |

|                 | 3.1          | Methods                           | 22                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 3.1.1 Lithography                 | 22                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 3.1.2 Image reversal              | 23                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 3.1.3 Graphene transfer           | 25                                                                                                                                                                                                                              |  |  |  |  |

|                 | 3.2          | Devices                           | 26                                                                                                                                                                                                                              |  |  |  |  |

|                 | 3.3          | Processing                        | 28                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 3.3.1 Graphene gate               | 31                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 3.3.2 ITO gate                    | 35                                                                                                                                                                                                                              |  |  |  |  |

| 4               | DIO          | DDE CHARACTERISATION              | 37                                                                                                                                                                                                                              |  |  |  |  |

|                 | 4.1          | Current - voltage (IV)            | 37                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.1.1 Measurement                 | 37                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.1.2 Results and discussion      | 43                                                                                                                                                                                                                              |  |  |  |  |

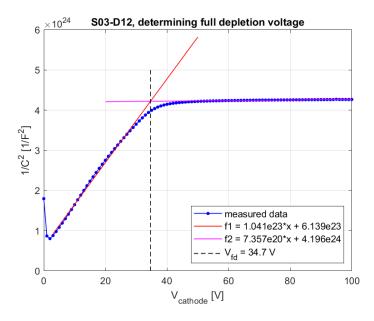

|                 | 4.2          | Capacitance - voltage (CV)        | 54                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.2.1 Measurement                 | 54                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.2.2 Results and discussion      | 57                                                                                                                                                                                                                              |  |  |  |  |

|                 | 4.3          | Transient current technique (TCT) | 58                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.3.1 Measurement                 | 58                                                                                                                                                                                                                              |  |  |  |  |

|                 |              | 4.3.2 Results and discussion      | 61                                                                                                                                                                                                                              |  |  |  |  |

|               | 4.4 | Radiation |                        |    |  |  |

|---------------|-----|-----------|------------------------|----|--|--|

|               |     | 4.4.1     | Measurement            | 62 |  |  |

|               |     | 4.4.2     | Results and discussion | 64 |  |  |

| 5 CONCLUSIONS |     |           |                        |    |  |  |

| REFERENCES    |     |           |                        |    |  |  |

## LIST OF ABBREVIATIONS

$Al_2O_3$  aluminum oxide

ALD atomic layer deposition

BOE buffered oxide etch

CSA charge sensitive amplifier

CV capacitance-voltage characteristics

CVD chemical vapor deposition

DIW deionized water

EQE external quantum efficiency FWHM full width at half maximum

Gr graphene

HIP Helsinki Institute of Physics

IPA isopropanol/2-propanol

ITO indium tin oxide

IV current-voltage characteristics

LCD liquid crystal display LED light emitting diode

MCA multichannel analyzer

MIC metal ion containing

MIF metal ion free

MOS metal-oxide-semiconductor

NaOH sodium hydroxide

OLED organic light emitting diode

PCB printed circuit board

PIN structure of p-type layer, intrisic layer and n-type layer

PMMA polymethyl methacrylate

$SiN_x$  silicon nitride  $SiO_2$  silicon dioxide

SMU source measurement unit TCT transient current technique

UV ultraviolet

VMU voltage measurement unit

## LIST OF SYMBOLS

A area

C capacitance

$E_q$  energy

$E_F$  Fermi energy

$E_g$  energy of band gap  $E_i$  ionization energy  $\varepsilon$  total permittivity ER energy resolution

I current

$J_{bulk}$  current density in the bulk  $J_{surface}$  surface current density

$\lambda$  wavelength N charge density

P perimeter

q charge of an electron

$R_C$  contact resistance  $R_S$  sheet resistance  $R_T$  total resistance  $V_{bias}$  bias voltage

$V_{FB}$  flat band voltage

$V_{fd}$  full depletion voltage

$V_G$  gate voltage

$V_T$  threshold voltage

W width

w capacitor thickness

## 1 INTRODUCTION

## 1.1 Background

Semiconductor industry is nowadays very large and silicon has been the main enabler for that. Silicon detectors have been developed for decades, the goal being to fabricate detectors with smaller leakage current and thinner dead layers to maximise the radiation response. The main problems with silicon detectors are radiation damage and performance degradation, but the small size, good energy resolution and fast detection have been the driving forces to develop detectors to overcome the problems [1].

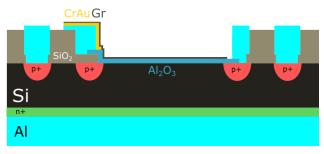

In this thesis the process of fabricating and characterization of gated induced junction silicon diode detectors is described. Induced junction works like pn-junction but instead of doping it is based on field effect passivation. The inversion layer is created with charged oxide which attracts minority charge carriers in semiconductor bulk to the surface. Induced junction photodiode and the working principle of induced junction was first time reported in 1978 [2]. The gate is a conductive material deposited on top of the diode active area which is biased to control the inversion layer in the semiconductor.

The motivation for the fabrication of these diodes was testing out passivation techniques with induced junctions and gates. For gates, graphene and indium tin oxide (ITO) were chosen. The advantage of using induced junction is minimizing the dead layer on top of the active area of the detector. Dead layer consists of everything that is on top of the active area (in this case silicon bulk). Problem with dead layer is that it absorbs some of the radiation entering the detector but does not act as a detecting medium. Thick dead layer can cause significant energy loss [1]. The passivation layer is only tens of nanometers thick and there is no dead layer in form of doped area. To minimize the thickness of dead layer, the gate materials were chosen to be as thin as possible. Graphene is only one atom layer thick which means it should not suppress the radiation entering the detector like thicker metal layer would.

## 1.2 Objectives and delimitations

The main goal of this thesis is to find out if the gate gives an advantage on the operation of the induced diode detector. A set of four wafers is fabricated, each of them having slightly different back-end processing steps (or no back-end processing at all). The wafer

design includes five different types of diodes that can be compared to each other. Gates are fabricated on two wafers to test two different gate materials. For gate materials, testing graphene (Gr) was the main interest and the wafer with indium tin oxide (ITO) gates was fabricated to be a reference for that. Both gate materials are transparent which allows testing the detectors with visible light.

The induced junction is based on the oxide having a strong charge that induces an inversion layer into the silicon surface. The inversion layer is comparable to pn-junction made with traditional doping of silicon. Usually the induced junction is created by having lightly doped wafer with majority charge carriers having the same charge than in the oxide. Most common combinations are p-type silicon and  $SiO_2$ , and n-type silicon and  $Al_2O_3$ . In this thesis the focus is on the latter one.

When a gate electrode is deposited on top of the charged oxide, the electrode can be biased to cancel or to boost the charge in the oxide and that way change the state of the induced layer. The focus in the measurements was to observe the effect of gate biasing for detector operation.

In this thesis the whole process of fabricating the diodes is described, starting from the silicon wafers and continuing into characterisation of the final devices. The design and structure of diodes is already defined because front-end processing is already done. Front-end processing steps include the fabrication of the diodes with metal contacts and back-end processing includes the gate fabrication. The fabrication is done in VTT Micronova cleanroom in Espoo.

The characterisation includes four types of measurements: current-voltage (IV), capacitance-voltage (CV), transient current technique (TCT) and radiation. The first two, IV and CV, focus on measuring the detector properties in the dark to get an idea about the leakage current of the detector. The latter two (TCT and radiation) focus on the detector operation with different radiation sources: visible light (red laser) in TCT and gamma rays in radiation measurements.

The main focus for characterisation is on IV measurements. Large number of different types of diodes are measured from several wafers to be able to compare and find out the differences. Having several wafers that have same design will show the differences caused by differences in fabrication steps. Being able to measure different types of diodes from same wafer will be good for comparing different diode types. Majority of IV measurements is done at VTT Micronova in Espoo.

CV, TCT and radiation measurements are done at Helsinki Institute of Physics (HIP) Detector Laboratory at Kumpula campus of University of Helsinki. For these measurements only limited amount of diodes are measured, the focus being in the induced junction diodes with gate. In TCT and radiation measurements the focus is to check that the diodes actually work as detectors, and possibly get an idea about how good detectors they are or how the design could be improved.

## 1.3 Structure of the thesis

The thesis starts with description of most important properties of semiconductors and description of semiconductor detectors in chapter 2. In the chapter 3 most important techniques and the fabrication process are described. The chapter also includes fabrication results. Chapter 4 focuses on electrical characterisation of components fabricated in previous section. Four different types of measurements are described: current-voltage (IV), capacitance-voltage (CV), transient current technique (TCT) and radiation. Each measurement type is presented as its own section, starting with description of the measurement technique and setup and then moving into the results and discussion. In chapter 5 the conclusions from the results are given.

## 2 BASICS OF SEMICONDUCTOR DETECTORS

Semiconductor materials are the basis of the microelectronics industry and also very important materials for solid state detectors. In detector applications, semiconductor detectors have several advantages: their energy resolution is remarkably better when compared to other types of detectors (gas filled or scintillation detectors), they are small, size can be varied and the detection is fast. These properties make semiconductor detectors good for radiation detection. Of course, like all detectors, also semiconductor detectors have properties that make them non-ideal, like performance degradation and radiation damage after long term use. [1]

In this section the basic properties of semiconductors and semiconductor detectors are discussed, starting from properties of semiconductor materials and from there moving to pn-junctions and semiconductor detector structures.

#### 2.1 Semiconductor materials

The electrical properties of solid state materials are based on the material energy band structures. Energy bands are based on quantized electron energies: electron energy must be on allowed energy level. When considering semiconductors, three bands are important: valence band, conduction band and forbidden gap between previous two. Electrons can only be in valence band or in conduction band. Solid state materials can be divided into three categories based on their energy band structures: metals, insulators and semi-conductors.

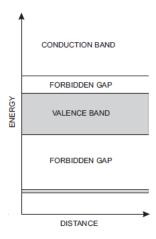

Metals conduct electricity well because there is no band gap between valence band and conduction band, and electrons are free to move. In insulators and semiconductors the outer shell electrons are in the valence band and their movement is restricted by forbidden gap. Insulators are very poor conductors, because the energy gap is wide (at least 5 eV). That means that electrons need to gain high energy to be able to move from valence band into conduction band. Semiconductors also have a band gap, but it is considerably lower than for insulators, around 1 eV, depending on the material. Semiconductor energy band structure is shown in figure 1, taking also the core energy band into account. Low band gap means that it is easier for electrons to move to higher energy states than it is in insulators. The conductivity of semiconductor materials is limited when compared to metals as the movement of electrons is restricted because of the band gap. [1]

Figure 1. Energy band structure in semiconductors. From [3].

Most commonly used semiconductor materials in detector applications (and overall in any semiconductor applications) are silicon (Si), germanium (Ge) and gallium-arsenide (GaAs). Many other materials are also researched but none of them have reached the same popularity as those three. Silicon and germanium both have diamond lattice structure and have four valence electrons, which means that they belong to group IV in the periodic table. The valence electrons forming covalent bonds with neighboring atoms are the basis for doping. [3]

Valence electrons in covalent bonds can be excited from valence band into the conduction band. This excitation can happen thermally or by radiation, such as visible light or charged particles. When a valence electron moves up to a conduction band, it leaves behind a vacancy in the valence band. That vacancy is called hole. Electrons and holes are the charge carriers in semiconductor materials, electron having a net negative charge and hole having a net positive charge. When electron moves from valence band up to conduction band, it forms an electron-hole pair. Formation of electron hole pairs is the basis for semiconductor detector operation. Electron-hole pairs can form at any non-zero temperature but they are more likely to happen if an electric field is present. Without electric field the thermally excited electron-hole pairs recombine leading to equilibrium. [1]

The previous descriptions are about intrinsic semiconductors, pure semiconductor materials without any impurities or dopants. In intrinsic semiconductors the density of charge carriers is relatively low (about  $10^{10} \, \mathrm{cm}^{-3}$  in silicon in room temperature [1]). To improve the conductivity of the material, dopant materials can be added into the semiconductor material. Depending on what type of charge carriers are wanted, dopant materials for silicon are from either group III or group V elements from the periodic table. After doping the majority charge carrier concentration can be several magnitudes higher compared to

intrinsic semiconductor ( $10^{12}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup> [3]) and the minority charge carrier concentration is several magnitudes lower compared to intrinsic charge carrier concentration.

Elements from group III have three valence electrons, one less than silicon. Semiconductor doped with group III element is called p-type as the majority charge carriers are holes with a positive charge. Group V elements have five valence electrons which means that after forming a bond with silicon there is one extra valence electron. Material doped with group V atoms is called n-type because majority charge carriers are electrons with a negative charge. The most common material used for p-type doping is boron (B) and for n-type doping it is phosphorus (P). The free charge carriers form their own level inside the forbidden band. In the case of p-type material this acceptor level is close to valence band and in the case of n-type material the donor level is close to conduction band. The electrons in these levels are more loosely bound to atoms and can move more freely in the material.

Another parameter related to band gap structure is Fermi energy,  $E_F$ . Fermi energy tells about the chemical potential in the material. In intrinsic semiconductor the Fermi level is in the middle of the forbidden gap in between valence and conduction bands. With doping the Fermi level moves closer to the formed acceptor or donor level. [3]

The energy needed to excite electron from valence band into conduction band depends on the band gap energy of the material. That energy can be approximated from

$$E_i \approx 2.6E_a + 0.6 \text{ eV}, \tag{1}$$

where  $E_i$  is the ionization energy and  $E_g$  is the size of band gap. Silicon band gap is  $1.12 \,\mathrm{eV}$  and the energy needed to excite an electron from valence band into conduction band is  $3.6 \,\mathrm{eV}$ . For detector applications low ionization energy is an advantage because it allows detecting particles with lower energies. For many other types of detectors, like scintillators or gas detectors, excitation energies are tens of  $\mathrm{eV}$ . [1], [3]

## 2.2 PN-junction

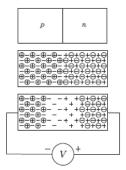

Joining together n- and p-type semiconductor materials forms a pn-junction which is the basis for semiconductor detector operation. When parts with different types of charge carriers are joined together, automatically the free charge carriers are attracted to the opposite side where they recombine. That creates an area with fixed charges to both sides

**Figure 2.** Pn-junction and formation of the depletion region in reverse biased pn-junction. From [3].

of the junction called depletion region. Depletion region is always formed when the pnjunction is present, but it can be controlled by applying voltage to the junction. When positive voltage is applied to p-type material and negative to n-type the current flows freely through the junction. This is called forward biasing. In detector applications the junction is biased to have negative potential to p-type side and positive potential to n-type side of the junction. This is called reverse biasing and is shown in figure 2.

The energy band structure in different biasing schemes is shown in figure 3. Without applied voltage between differently doped regions the potential difference is equal to the built in potential and the energy bands have bent to create constant Fermi level. When forward bias is applied, the band bending is decreases. That means that the potential difference between valence and conduction bands is smaller than the built in potential. In the case of reverse bias the energy bands bend even further, compared to thermal equilibrium. That leads to depletion region extending further as the potential difference on different sides of the junction increases. [3]

In reverse biasing the width of the depletion region is increased as the free charge carriers are attracted to opposite side of the junction. In reverse biased mode the depletion region acts like a capacitor because the resistance of the depletion region is high. When radiation entering the detector creates electron-hole pair, the charge carriers are quickly collected to opposite sides of depletion region. Detector operated in reverse biased mode, without any radiation present, has very low current flow. The current getting through the reverse biased detector is called leakage current. Minimizing the leakage current is important part of the detector design and fabrication, as it should be remarkably lower compared to measured signal. [1], [3]

Figure 3. Energy bands inside the pn-junction in different biasing schemes. From [3].

#### 2.3 PIN diode as radiation detector

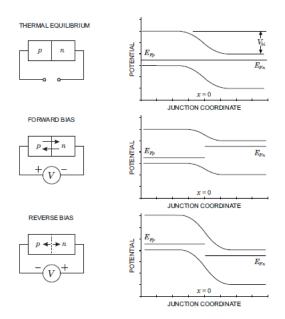

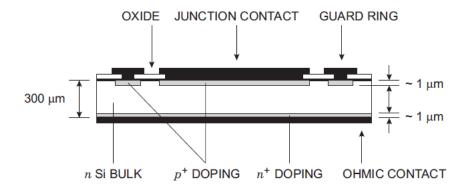

PIN diode is a common structure for semiconductor detector applications. Basically PIN diode is heavily p- and n-doped layers with an intrinsic bulk layer between them. Technically it is not possible to have completely intrinsic silicon and because of that the bulk is lightly n- or p-doped. In figure 4 is shown the basic PIN diode structure with n-type silicon bulk. The detector entrance is in the middle of the topside (junction contact in fig. 4) and on both sides of that junction are shown smaller junctions, called guard ring. The role of guard ring is to prevent unwanted current from substrate edges from entering the detector. The guard ring and the contact to the front side of the junction (anode in case of p+ doping) are biased to the same potential. The active area of the detector is the bulk between doped layers. The active area extends to about halfway through the space between junction contact and guard ring.

The entire backside of the detector is coated with metal to create ohmic contact. For measurements or detector operation, the bias is supplied to the detector from the backside. Depending on the type of used material, the junction contact and guard ring are set to either higher or lower potential than the backside.

As was already mentioned in previous section, semiconductor detectors are operated in reverse biased mode, often biased to have the depletion region to reach through entire bulk (fully depleted). The full depletion voltage  $V_{fd}$  is important parameter for detectors as it defines in what voltage range the detector can be operated. The full depletion voltage of

Figure 4. Structure of basic PIN diode detector. From [3].

the detector depends on the quality of the substrate. For high resistivity wafers with only small amounts of impurities and low doping concentration the full depletion voltage is lower than for wafers with lower resistivities. Common resistivities for detector applications are 1-10 k $\Omega$  cm. [4] In figure 4 the detector thickness is shown to be 300  $\mu$ m, which is common thickness for silicon detectors because the  $V_{fd}$  does not become too high with resistivities <5 k $\Omega$  cm.

PIN diode can be used to detect different kinds of radiation, like charged particles or visible light. The energy needed to create one electron-hole pair in silicon is approximately 3.6 eV, as was mentioned earlier. Charged particle passing through the detector will create several electron-hole pairs which are swept by applied electric field to edges of the detector where the charge carriers induce a current into the metallic contacts. The detection is most efficient when detector is operated in fully depleted mode as then the entire silicon bulk will act as detecting media and the electric field extends through the entire wafer, making collection of the charge carriers more efficient. When the purpose is to detect visible light, the materials and the thickness of dead layer become more important because of the short wavelength and low energy of photons. Photon energy is enough to create only one electron hole pair after entering the detector. [1], [3]

## 2.4 Induced junction

Silicon surface passivation has been important part of any semiconductor device processing for several decades. In induced junction the passivation is utilized to create inversion layer to reduce the dead layer on top of the detector active area. The most common way to achieve surface passivation is by depositing thermal  $SiO_2$  layer on the wafer to prevent the surface recombination losses. The  $SiO_2$  surface passivation is based on reducing

the density of states at the Si-SiO<sub>2</sub> interface. With materials with higher fixed charge the passivation is based on field effect passivation. Materials with high fixed charge are  $Al_2O_3$  (large negative fixed charge,  $10^{12}$  cm<sup>-2</sup> to  $10^{13}$  cm<sup>-2</sup> after annealing [5], [6]) and silicon nitrides (SiN<sub>x</sub>, large positive charge). [7] The charge in SiO<sub>2</sub> is lower,  $10^{10}$  cm<sup>-2</sup> to  $10^{12}$  cm<sup>-2</sup> after annealing [8], [9].

Induced junction is like traditional pn-junction but instead of doping the junction is formed by having charged oxide induce an inversion layer to the surface of the substrate. The first induced junction photodiode was introduced by Hansen in 1978 [2]. They presented a way to create n-type inversion layer to p-type silicon wafer using  $SiO_2$ . The positive charge in  $SiO_2$  attracts electrons to the surface and when the electron concentration at the surface is equal or larger than the hole concentration in the bulk, inversion layer can be formed. Ohmic contact to the inversion layer is created by having a doped ring around the active area (n+ doping in the case of p-type silicon). [2]

The early publications about induced junction diodes focused on p-type substrates and  $SiO_2$  passivation. As the induced junction needs the charged oxide have same charge as majority charge carriers in semiconductor bulk, forming inversion layer with  $SiO_2$  does not work in a same way for n-type silicon substrates. Induced junction photodiodes using n-type silicon wafer as a substrate were reported by Juntunen *et al.* [10]. They used  $Al_2O_3$ , which has large negative charge, to create the induced junction. To increase light collection efficiency the surface of their photodiode was nanostructured to have black silicon underneath the  $Al_2O_3$ . Alpha particle detector utilizing  $Al_2O_3$  induced junction was presented in recent master's thesis with promising results [11].

The advantage of induced junction is thinner dead layer (compared to traditional pnjunction) which means that less radiation is absorbed in it. The thickness of dead layer is critical for detecting UV-light due to short wavelength. External quantum efficiency (EQE) is parameter for presenting the quality of a photodiode, it is defined as a ratio between collected charge carriers and the photons incident to he device. Induced junction photodiodes are reported to have good response on wide range of visible light wavelengths (200-1000 nm) and especially in UV range (<400 nm) [2], [10]. The induced junction photodiodes with black silicon were reported to have EQE over 96 % over entire visible light spectrum without applying bias [10]. Another issue with UV photodiodes has been the degradation of the detector after long exposures to UV radiation. Induced junction detectors have been shown to handle well the exposure to UV radiation [12], [13].

#### 2.5 Gated diode

In gated diode additional metal (or other conductive material) layer is added to the diode. By biasing the gate the surface states of the diode can be changed. The operation of gate is based on having surface passivation and controlling the field effect passivation with the voltage applied to the gate. Diodes with gates has been utilized for studying the leakage current and extracting different components of the leakage current since 1960s [14]. The gate on diodes used for leakage current analysis has been on the edges of the traditional pn-junction and the gate is used to create inversion layer that continues further in the silicon surface than the original junction. For that kind of gated diode operation the diode is in accumulation state until the gate bias is large enough to create inversion layer. This kind of gated structure with gate on the sides of the junction is tested with PIN structure for radiation detection [15], [16].

With induced junction the basic of operation is same as described above, and the gate is placed on top of passivating oxide, in the case of this thesis  $Al_2O_3$  layer. The structure is similar to MOS-capacitor (metal-oxide-semiconductor). But because the junction in the active area is now induced junction instead of doped, the gate is used to control the state of the induced junction. When voltage is applied to the gate, depending on the polarity and magnitude of the bias there are three possible states for the MOS capacitor; accumulation, depletion and inversion. These states are basically same also for the gated diode.

As the three layers of MOS structure are joined together, all materials have different potentials or charges. That causes bending of the band gaps which leads to different states. At certain voltage the Fermi level is uniform through all three layers. The voltage used to achieve this condition is called flat band voltage  $(V_{FB})$  and it can be used to determine the three other states. [17] The states are

- 1. accumulation  $(V > V_{FB})$

- 2. depletion  $(V_{FB} < V < V_T)$  and

- 3. inversion ( $V \ll V_{FB}, V \ll V_T$ ).

$V_T$  in threshold voltage between depletion and inversion. In accumulation the gate voltage is higher than the flat band voltage which means that the majority charge carriers are attracted to the surface of the semiconductor. The depletion happens when the gate voltage has the same polarity as the majority charge carriers attracting the minority charge carriers

into the semiconductor surface. When the gate voltage is large enough to attract minority charge carriers to the surface in such large population that an inversion layer is formed, the diode is in inversion. [4], [17]

The oxide considered for MOS capacitors is often  $SiO_2$ , which has relatively low charge, especially when compared to doping concentrations or to charge in the  $Al_2O_3$ . In the case of  $Al_2O_3$  with n-type silicon the inversion layer is strong even without applying voltage. The oxide charge and the thickness of the oxide have an effect to the threshold voltage  $V_T$ .

Two materials were tested for gates for induced junction diodes: graphene and indium tin oxide (ITO). The main criteria for choosing these materials were their transparency and the minimal thickness to reduce the dead layer. Both properties are important for detecting visible light.

#### 2.5.1 Graphene

Since single layer graphene was first time demonstrated in 2004 [18], it has gained huge amounts of attention because of its unique properties. Graphene is only one atom layer thick with honeycomb lattice and it has semimetal properties with slight overlap of valence and conduction bands in its natural state [18]. That means that graphene has high conductivity and it can be used as an electrode in some applications but it can also be used as a semiconductor. Graphene does not have a natural band gap. Zero band gap, monolayer structure and the high mobility,  $10\,000\,\mathrm{cm^2/Vs}$  [18], compared to electron mobility of Silicon (1350 cm²/Vs [1]), makes graphene attractive material to be used in semiconductor applications. Graphene has been used as an electrode and as semiconductor in many forms in different applications, like solar cells, field effect transistors (FETs), light emitting diodes (LEDs) and modulators [19], [20].

Again, the monolayer structure of the graphene makes it interesting material for diode gate material. For detector purposes minimizing dead layer on top of active area is important to keep energy absorption in dead layer in minimum [1]. Graphene is only one atom layer thick, the thickness being few Ångströms, metal gate (like Al) would add at least tens of nanometers or even more on top of the detector active area. For photosensitive devices another criteria for good gate material is optical transparency. Graphene absorbs 2.3% of white light and the absorption does not vary noticeably between different wavelengths [21]. Graphene has been successfully used as an transparent electrode in perovskite solar

cells [22], which is promising result while considering graphene for gate material.

## 2.5.2 Indium tin oxide (ITO)

ITO, indium tin oxide, is commonly used transparent conductive oxide. It is n-type semi-conductor material that has wide band gap, about  $4\,\mathrm{eV}$  (can be tuned to be higher), and low resistivity,  $<10^{-4}\,\Omega\,\mathrm{cm}$  [23]. The transmittance of ITO films is  $>80\,\%$  and values up to  $95\,\%$  have been reported. ITO can be deposited by many different methods like magnetron sputtering, molecular beam epitaxy, thermal evaporation and pulse laser deposition. [24] It has been demonstrated that by altering sputtering parameters it is possible to change the properties of ITO film, like the optical transmittance and the conductivity [25]–[27]. The applications of ITO include flat panel liquid crystal displays (LCD), organic light-emitting diodes (OLED), solar cells and many more.

## 3 DIODE FABRICATION

## 3.1 Methods

In this section few of the most critical processing methods, photolithography and graphene transfer, are introduced. Only these two methods were chosen to be introduced in more detail, because those were the most important ones for the processing that was done for this thesis. The more technical details are given later, the purpose of this section is to give a bit more background information to those methods.

## 3.1.1 Lithography

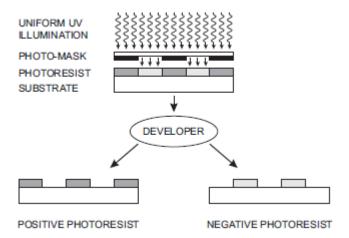

Photolithography is a method that is used for creating patterns to the wafer and to protect areas that are not processed during that step. The lithography process includes spin coating, exposing and developing photoresist on the wafer. After the processing step is finished, the resist is removed. The basic lithography process is shown in figure 5.

**Figure 5.** The basic process of lithography for positive and negative photoresists. Picture from [3].

Photoresist is photosensitive material and when it is exposed to ultraviolet (UV) light, the structures of the material change. There are two types of photoresists, positive and negative. When positive resist is exposed, it becomes easily soluble to developer. With negative resist the exact opposite happens, as the exposed resist becomes harder and non-soluble. [3]

For exposure there are several options. The most common one, and also the one used in this thesis, is using a mask aligner with mercury lamp and a mask, that has the pattern of entire wafer. Other options are using a stepper or a laser writer. Stepper also uses mask, but it is smaller and the wafer is exposed a part at the time. With laser writer the pattern is exposed pixel by pixel using laser. [28]

There are two types of photomasks: light field and dark field masks. Light field masks have the pattern made from opaque material and rest of the mask is clear. Dark field masks have the negative of the pattern, the mask is opaque and the structures are open. The polarity is chosen to fit the purpose of the mask.

After the exposure the resist is developed. Development is final step before the pattern is finished. If the resist is positive tone, the exposed parts are dissolved into developer, and with negative tone resist unexposed parts are dissolved. Development solutions are generally divided into metal ion containing (MIC) or metal ion free (MIF). MIC developers are often based on NaOH or KOH. Sodium (Na) and potassium (K) are harmful for semiconductors which means that using developers containing them should be avoided in semiconductor detector processing. Many developers attack aluminum or other alkaline sensitive materials. Because of these reasons for wafers processed as a part of this thesis the used developer was MIF type which does not attack aluminum. The development can be done by immersing wafer into a tank or a beaker filled with developer or on a track. On track based processing options are puddles or spray. The development rate (μm/min) is given in developer data sheet. [29]

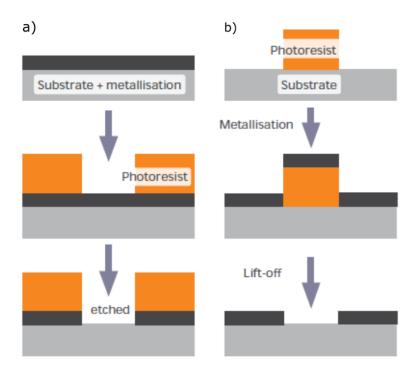

Two most common ways to use lithography are shown in figure 6. Etching process is shown in figure 6a. In etching process the metal deposition is done first and the resist is applied on top of it. Then the metal is etched from the resist openings, using wet or dry etching, and resist is removed. The lift-off process is shown in figure 6b. In lift-off process the patterning is done first and then the metal is deposited everywhere. After resist removal, metal that was deposited on top of the resist comes off leaving patterned metal to the wafer.

#### 3.1.2 Image reversal

For lift-off it is possible to use image reversal technique to get undercuts to ensure best possible results after removing the resist. Image reversal resists behave like positive resists if few special steps are not taken during the lithography process. After the reversal process

**Figure 6.** Two basic process flows for lithography a) wet etching and b) lift-off. Picture from [30].

the result is negative pattern. It is also possible to use normal positive or negative resist for lift-off, but the properties of image reversal resist are better for the purposes of the lift-off. The undercuts, which make the resist removal process easier, are possible only with negative or image reversal resists. Ideally, positive resists have straight sides but in practice the sides are sometimes over-developed. The purpose of undercuts is to make sure that there is some open resist after metal deposition. If all of the resist is fully covered in metal, the lift-off does not work. Negative resists form harder bonds, which means that they can handle higher temperatures, but that also means that the resist is harder to remove [30].

Image reversal has few additional steps compared to basic lithography process. In the work done for this thesis, same positive AZ 5241E resist is used for image reversal process.

Image reversal starts with resist spinning and exposure with mask. The exposure is followed with reversal bake at stable temperature. The reversal-bake is the most critical step in the process and to ensure consistent results, it is best to use hotplate. With hotplate it is easier to set temperature to right value and keep it within needed limit of  $\pm 1^{\circ}$ C [31] from the set temperature. The recommended reversal-bake temperature is  $120^{\circ}$ C for 2 minutes [31], but for the work done for this thesis  $110^{\circ}$ C for 2 minutes was found to be the most suitable. During reversal bake the exposed parts of the resist crosslink and

become unsoluable in the developer.

Another additional step in image reversal process is flood exposure. In the flood exposure the wafer is exposed to high dose of UV light. The dose can vary within range of 150-500 mJ/cm<sup>2</sup>. The recommended dose for AZ 5214E resist is 200 mJ/cm<sup>2</sup>. [31] After the flood exposure the wafer is developed the same way it would be without image reversal steps.

## 3.1.3 Graphene transfer

Chemical vapor deposition (CVD) is the most common way of growing graphene sheets on top of metal substrates, often on copper substrates. During past fifteen years many different methods have been used to transfer graphene from the growth substrate to the target substrate. Generally the methods can be divided into two categories: etching and etching-free transfer.

In etching transfer the metal substrate is etched away. Etching is done either before or after the actual transfer, depending on the method. In intact transfer graphene is protected with supporting layer. Commonly used supporting layer material is polymethyl methacrylate (PMMA) resist, which creates a flexible but mechanically strong protection layer that is easily removed with solvents. Other etching transfer method is clean transfer, in which the graphene is transferred directly from the growth substrate to the target substrate and then the growth substrate is etched away. Clean transfer methods were developed to get rid on polymer residues in graphene after transfer. [32]

In etching-free transfer the graphene sheet is peeled away from the growth substrate either mechanically or with electrochemical bubbling. Mechanical delamination is a dry method for transferring graphene. It is based on forming a bond between graphene and the target substrate. The bond can be formed either with an adhesive that stays between graphene and target substrate or with stamping method. In stamping method the graphene is first removed from the growth substrate with help of other substrate and from there it is released to target substrate. [32] In electrochemical bubbling the graphene sheet (protected with layer of PMMA) is released from the growth substrate in aqueous solution using the growth substrate as cathode. Bubbling transfer is fast method, delaminating the graphene in only seconds when etching the substrate can take hours [33]. The bubbling transfer is also reported to have graphene films free of metal contamination from the growth substrate [32].

Bubbling transfer is based on electrochemical reaction of water reduction creating hydrogen bubbles at the interface between graphene and the metal film. The graphene (usually covered with PMMA) peels off from the growth substrate and floats on top of the electrolyte. The bubbling transfer was first introduced by Wang *et al.* in 2011 [34]. They used aqueous solution of  $K_2S_2O_8$  as electrolyte, CVD grown graphene on copper foil, protected with PMMA layer, as their cathode and glassy carbon as an anode. The entire process took about 60 minutes. The process was not fully etching-free as some chemical etching was observed during the bubbling process.

The first fully etching-free method was reported in 2012 by Gao *et al.* [33]. It was remarkably fast compared to bubbling process presented in [34] and to traditional etching methods, because the delamination of graphene-PMMA stack happened in tens of seconds. In the initial work, platinum (Pt) was used as the growth substrate, but the method works also with other substrate types. Aqueous solution of NaOH (sodium hydroxide) was used as electrolyte, the Pt substrate with graphene and PMMA was used as cathode and a piece of Pt foil was used as anode. The Gr-PMMA stack was cleaned with deionized water (DIW) and then transferred to Si/SiO<sub>2</sub> substrate. This method was the one used for graphene transfer in the work done for this thesis. The use of NaOH in bubbling might leave some traces into the graphene film which could cause some problems in the semiconductor.

#### 3.2 Devices

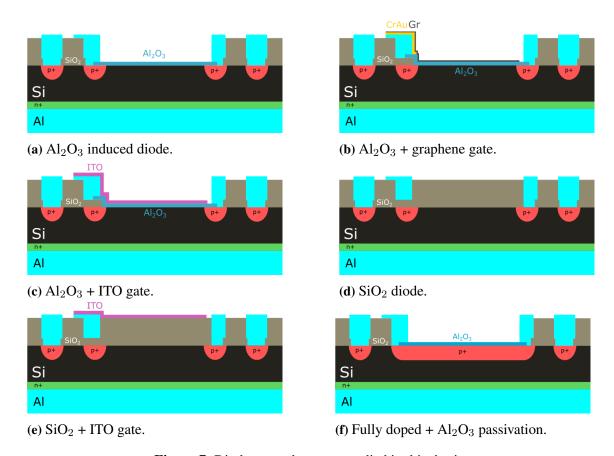

The focus of the thesis is centered around  $Al_2O_3$  passivation, induced junctions and gated diode structure. Especially induced junctions and gated diodes are not yet very common structures for detectors, as was discussed in section 1.1. In order to have something to compare results from these more unconventional structures there needed to be also more traditional structures. For that reason there were quite many different variations included into the design.

The "basic diode" was round diode with active area  $1650\,\mu\mathrm{m}$  active area diameter and in the design there are several variations to that diode. The variations are

- Al<sub>2</sub>O<sub>3</sub> induced junction diode (fig. 7a),

- Al<sub>2</sub>O<sub>3</sub> induced junction diode with gate (graphene/ITO) (figs. 7b-7c),

- field oxide (SiO<sub>2</sub>) diode (fig. 7d),

- field oxide (SiO<sub>2</sub>) diode with gate (ITO) (fig. 7e),

- fully Boron implanted with Al<sub>2</sub>O<sub>3</sub> passivation (fig. 7f).

**Figure 7.** Diode types that were studied in this thesis.

In order to study the source of the leakage current, a further variation to the basic diodes were diodes with different active area diameters. The basic diameter is  $1650\,\mu\mathrm{m}$  and the variations were scaled up or down from that. This kind of diodes come with five different active area diameters:  $850\,\mu\mathrm{m}$ ,  $1150\,\mu\mathrm{m}$ ,  $1485\,\mu\mathrm{m}$ ,  $2475\,\mu\mathrm{m}$  and  $3300\,\mu\mathrm{m}$ . After measuring all five different sizes, it was possible to calculate the major source of leakage current (bulk or surface). The wafer design also includes different shapes of diode designs, but those diodes are not characterized in this work.

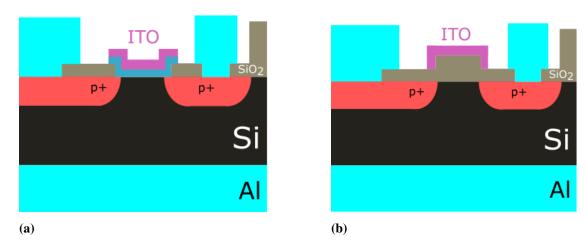

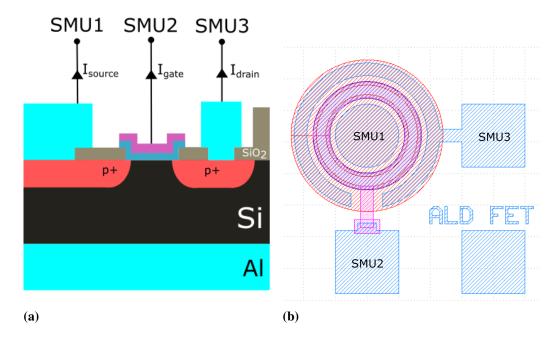

In addition to the diodes, that were the main interest in this work, the design included different types of FETs as test structures. To study the effect of gate and the contact between different layers, two types of FETs (figure 8) were measured:  $Al_2O_3$  under the gate (fig. 8a) and  $SiO_2$  under the gate (fig. 8b.

Figure 8. Cross sections of FET test structures a) Al<sub>2</sub>O<sub>3</sub> passivation, b) with SiO<sub>2</sub>.

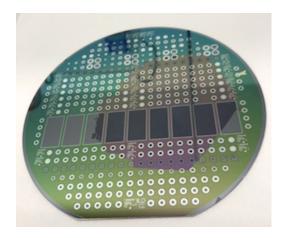

## 3.3 Processing

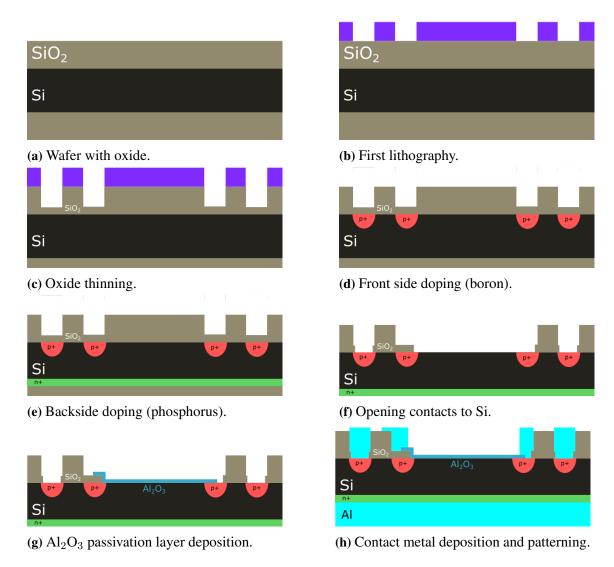

Detectors were fabricated on high resistivity silicon wafers, information about wafers is shown in table 3. The gate processing was done for wafers that had already all front-end processing steps done (steps 1-5 in table 3). Wafers presented in variation table 3 were part of a lot of 8 wafers, but only those four included in the table are relevant for the work done in this thesis. Front-end processing steps are shown in figure 9. The process started with wafer oxidation. For oxidation, the lot was divided and some of the wafers were sent out to external service provider, and some were oxidized in Micronova cleanroom.  $400 \, \mathrm{nm}$  thick oxide was grown to all wafers, dry oxide to the wafer oxidated at Micronova and wet oxide to those oxidated externally. Oxidation in Micronova was done in diffusion furnace Centrotherm E1200 HT 260-4. Oxidized wafer is the starting point for processing, shown in figure 9a.

The fabrication of diodes was started with first lithography (fig. 9b). Lithography tools

| Manufacturer        | Topsil GlobalWafers A/S            |  |  |  |

|---------------------|------------------------------------|--|--|--|

| Material            | High resistivity                   |  |  |  |

|                     | float zone (FZ) Silicon            |  |  |  |

| Diameter            | 150 mm                             |  |  |  |

| Thickness           | 675 μm                             |  |  |  |

| Type                | n (Phosphorus)                     |  |  |  |

| Crystal orientation | (1-0-0)                            |  |  |  |

| Resistivity         | $> 10 \mathrm{k}\Omega\mathrm{cm}$ |  |  |  |

| Finish              | double side polished               |  |  |  |

**Table 2.** Information about wafers that were used, provided by the manufacturer.

**Table 3.** Wafer variation table. Only wafers relevant for this thesis are included.

| Process step                      | O2 | <b>S</b> 1 | <b>S</b> 3 | S4 |

|-----------------------------------|----|------------|------------|----|

| 1. Oxidation                      |    |            |            |    |

| 1.1 Micronova (dry oxide)         | X  |            |            |    |

| 1.2 External (wet oxide)          |    | X          | X          | X  |

| 2. Implantations                  |    |            |            |    |

| 2.1 Front                         | X  | X          | X          | X  |

| 2.2 Back                          | X  | X          | X          | X  |

| 3. Oxide etch                     | X  | X          | X          | X  |

| 4. Al <sub>2</sub> O <sub>3</sub> | X  | X          | X          | X  |

| 5. Contact metal                  |    |            |            |    |

| 5.1 Front                         | X  | X          | X          | X  |

| 5.2 Back                          | X  | X          | X          | X  |

| Graphene gate                     |    |            |            |    |

| 6. Gate pads (Cr/Au)              |    |            |            |    |

| 6.1 Lithography                   |    |            |            | X  |

| 6.2 Evaporation                   |    |            |            | X  |

| 6.3 Lift-off                      |    |            |            | X  |

| 7. Graphene transfer              |    |            |            | X  |

| 8. Graphene patterning            |    |            |            | X  |

| 9.ITO gate                        |    |            |            |    |

| 9.1 Lithography                   |    |            | X          |    |

| 9.2 Sputtering                    |    |            | X          |    |

| 9.3 Lift-off                      |    |            | X          |    |

were same in all front-end processing steps. The resist coating was done on coater developer track EVG 120, exposures were done with Mask AlignerSuss MicroTec MA150 and development was done on developer track Convac M6000. All photomasks (for front-end and back-end processes) are quartz contact masks designed at VTT and ordered from Compugraphics Photomasks.

Lithography was followed with thinning the oxide to  $70 \,\mathrm{nm}$  (fig. 9c). The etch was done in buffered oxide etch (BOE) tank, O-wafers were etched for 4 minutes 15 seconds and S-wafers for 4 minutes and 25 seconds. The front side implantation of boron was done through thinned oxide (fig. 9d). In figure 9 is shown the process flow for  $Al_2O_3$  induced junction diode. Because of that the front side doping is only on guard rings. The entire backside was implanted with phosphorus (fig. 9e). Both implantations were done with Eaton NV8200 ion implanter.

**Figure 9.** Front end processing steps.

The second mask layer was for opening contacts to Si and the result after lithography process and wet etching in BOE (4 minutes, 30 seconds) is the structure in figure 9f. The third mask layer is passivation of the diode active area with 30 nm ALD (Picosun SUNALE R-150B) deposited Al<sub>2</sub>O<sub>3</sub>. The patterning was done after the deposition by wet etching in aluminum etch (main component phosphoric acid) at 40 °C for 18 minutes (fig. 9g). The final mask layer in front-end processing were depositing and patterning aluminum (Al) contact layers (fig. 9h). 300 nm of Al was deposited first on the front side of the wafer with OEM Mark Eclipse IV and after lithography it was patterned by wet etching in aluminum etch at 40 °C for 1 minute 50 seconds. The last step was to deposit Al layer also to backside of the wafer with the same sputtering tool.

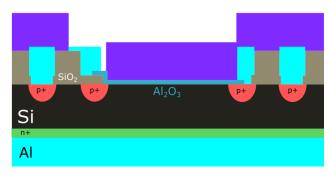

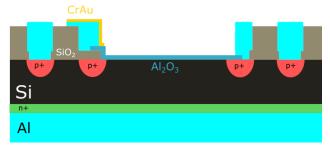

#### 3.3.1 Graphene gate

Graphene gates were continued on top of the steps shown in figure 9. Steps for fabricating the graphene gates are shown in figure 11. First step was to do lithography with image reversal (fig. 11a) for fabricating gate contact pads by evaporating chromium (Cr) and gold (Au) layers (fig. 11b). The processes described in this thesis are done in Micronova clean-room using Suss MicroTec Gamma 4 -resist track for spin coating, baking and developing. The used resist is AZ 5214E [31]. For exposures, mask aligner MA6 fron Suss MicroTec has been used, Evaporation was done with Instrument Mattila IM-9912 evaporator. The thickness of Cr layer was 15 nm and the thickness of Au layer was 30 nm. Finished pad is shown in figure 10. Additional metal layer on top of previously deposited aluminum pads was needed to make the step between the gate pad and graphene less steep. The height of aluminum pad is 300 nm and the thickness of graphene is only one atom layer, which causes it to break easily if the height differences are large.

**Figure 10.** Evaporated CrAu layer on gate contact pad after lift-off.

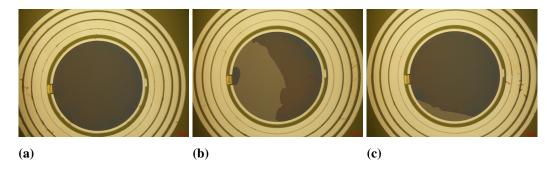

After doing the lift-off to finish gate pads 11c, the graphene transfer is done with bubbling transfer, the bubbling process is described in section 3.1.3. The graphene is CVD grown on copper substrate from Graphenea and it had a diameter of 100 mm. The graphene sheet was released from the copper substrate in aqueous NaOH solution and transferred to bowl of DIW. The graphene sheet was floating on top of water with PMMA layer being the topmost layer. To get the graphene sheet to wafer, the wafer needed to be slid underneath the graphene in DIW. Then the wafer was lifted up with the graphene, guiding the graphene to wanted area with help of tweezers. Then the wafer was left to dry. The placement of graphene on the wafer is shown in figure 12. The method used for transferring the graphene caused there to be a thick layer of water between the wafer and graphene. It took over 24 hours to get the wafer dry enough to continue processing. This long exposure to water caused some damage to Al<sub>2</sub>O<sub>3</sub> structures on the wafer.

The next step in the graphene transfer process was baking the wafer in resist oven (Memmert UFE 400). The wafer was in the oven for total of 45 minutes, temperature of the oven was increased every 15 minutes. The starting temperature was  $120\,^{\circ}$ C, then it was increased first to  $150\,^{\circ}$ C and finally to  $180\,^{\circ}$ C. Because the temperature was increased while keeping the wafer in the oven, the set temperature was reached only at the end of 15 minute interval (except  $120\,^{\circ}$ C, that was the oven temperature when the wafer was put in). During this first bake remaining moisture was removed underneath the graphene-PMMA stack.

After the first bake, the PMMA layer was removed. The wafer was kept for 4 minutes in acetone and 1 minute in IPA. The wafer was dried by blowing after taking it out of IPA, without dipping it into water first. Then the wafer was put to vacuum oven to 300 °C overnight. Purpose of keeping the wafer in the vacuum oven for a long time was to remove remaining PMMA particles and to increase the adhesion of the graphene to the wafer.

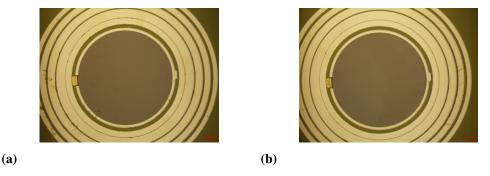

The final phase of graphene gate processing was patterning the graphene. Lithography was done with same AZ5214E resist as the other lithography layers. This time the resist was used in normal positive mode. Lithography results are shown in figure 13. Lithography parameters were not optimized for this process which lead to graphene ripping away from some of the gates during development (figures 13b and 13c). The graphene was etched in O<sub>2</sub> plasma (Oxford Instruments plasma stripper PRS900) for 5 minutes with 100 W power and 100 sccm oxygen flow. After etching the final step was removing the resist. It was done by keeping the wafer 15 minutes in acetone and then few minutes in IPA, again drying it right after it came out from IPA. Finished graphene gates are shown in figure 14. The figure 14b shows that even with microscope it can be difficult to see

which components have broken graphene.

(a) Lithography for lift-off.

(b) Evaporated contact metal.

(c) Contact pads after lift-off.

(d) Finished device with graphene gate.

Figure 11. Process steps for fabricating graphene gates.

Figure 12. The dark area is graphene after drying after the transfer.

Figure 13. Graphene gates after  $O_2$  etching, before removing resist. Darker areas have graphene and resist, from lighter areas the resist was ripped away during development.

Before starting chacterization the wafer was annealed (ATV PEO-603) in  $N_2$  at  $425\,^{\circ}$ C for 30 minutes. Annealing step was important to create contact between  $Al_2O_3$  layer and Silicon and activate the  $Al_2O_3$  layer passivation. Annealing in temperatures above  $400\,^{\circ}$ C have been shown to increase the charge in  $Al_2O_3$  (same goes also for  $SiO_2$ ) and increase the passivation [5], [6], [35].

Figure 14. Finished graphene gates: a) full graphene, b) broken graphene.

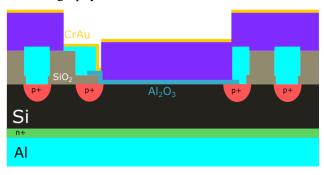

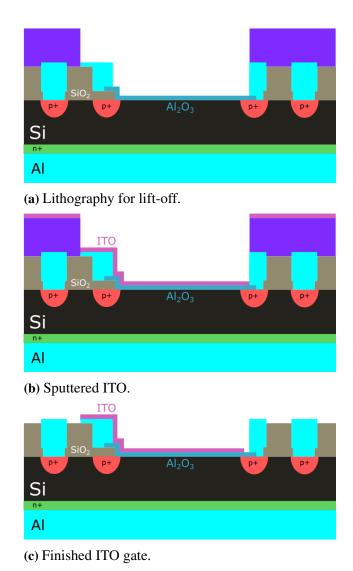

## **3.3.2** ITO gate

The wafer with ITO gates was processed to act as a reference for the graphene gated diodes. The processing was continued after steps shown in figure 9. The steps for fabricating ITO gates is shown in figure 15. ITO was fabricated with lift-off process and the first step was to do image reversal lithography (figure 15a), described in section 3.1.2. The ITO deposition was done with sputtering (VonArdenne CS 730 S Cluster System). The target thickness was  $50 \, \mathrm{nm}$ , sputtering power  $400 \, \mathrm{W}$  and sputtering time  $100 \, \mathrm{s}$ . The parameters were chosen based on previous experiments of sputtering ITO to achieve conducting film. The film thickness was checked after sputtering with spectroscopic ellipsometer Semilab SE-2000 and it was found to be about  $(38 \pm 5) \, \mathrm{nm}$  on a monitor wafer.

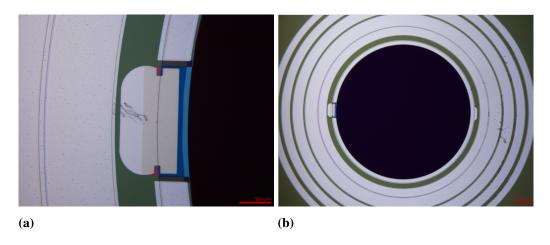

ITO gates were finished with lift-off (figure 15c). The wafer was 27 minutes in acetone, then it was transferred in IPA to posistrip, in which it was kept for 20 minutes. After rinsing with water the wafer was spindried. At the end the wafer was annealed at the same time with the other wafer,  $425\,^{\circ}\mathrm{C}$  for 30 minutes. Finished ITO gate is shown in figure 16.

Figure 15. Process steps for fabricating graphene gates.

Figure 16. ITO after lift-off: a) close up to the gate contact pad, b) finished gated diode.

## 4 DIODE CHARACTERISATION

After fabrication, the quality and the functionality of the detectors is tested with different types of measurement techniques. This sections is organized to subsections for different measurement types, in which the measurement setup and connections are described first, then followed by results and discussion.

# 4.1 Current - voltage (IV)

#### 4.1.1 Measurement

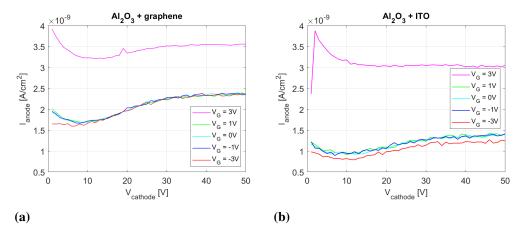

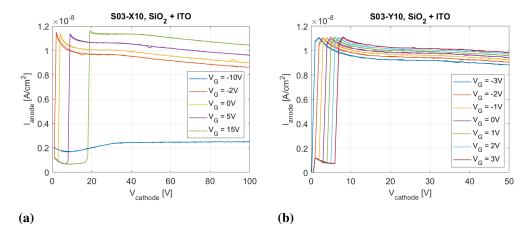

Current-voltage (IV) characteristics are important part of characterisation of semiconductor detectors. Reverse IV measurement done in dark (in case of light sensitive detectors) tells the level of leakage current in the detector. Semiconductor detectors are operated in reverse biased mode, as was explained in more detail in section 2. For diodes with n-type bulk studied in this thesis it means applying positive voltage to the backside (cathode) of the detector and negative voltage to the front (anode) of the detector and measuring the current from the anode. The reverse biasing increases the depletion region further into the silicon bulk. As there are no free charge carriers in depletion region (only charge carriers generated by heat or incoming radiation or caused by non-idealities of the material), the detector leakage current without light or radiation is very small. For good commercial PIN diode detectors the leakage current is order of 2-10  $\rm nA/cm^2$  [36], [37]. The level of leakage current tells about the quality of the detector: the smaller, the better.

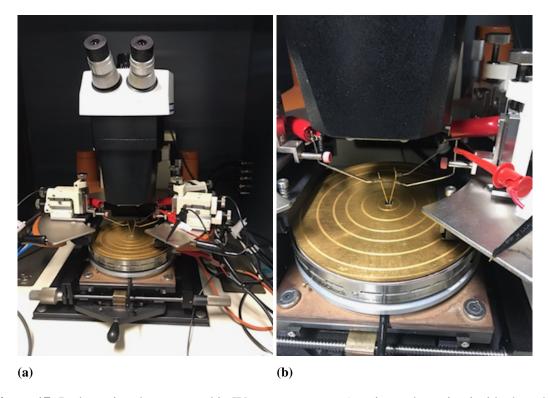

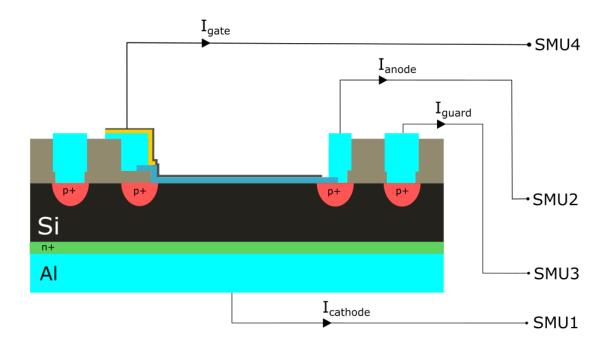

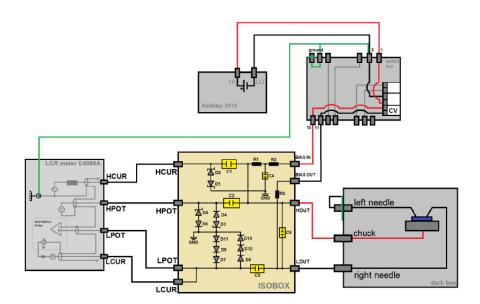

Major part of IV measurements was done at Micronova. The setup consists from manual probestation and Agilent 4155C/4156C parameter analyzer, which is connected to a computer through GPIB. The measurement is controlled with computer, using software programmed with MATLAB. The parameter analyzer has four source measurement units (SMUs) and two voltage measurement units (VMUs). For the most part, only SMUs are used for diode measurements. VMUs were used only in TLM measurements. The probestation, shown in figure 17a, is inside a cabinet, which has doors and additional cloth covering to ensure maximum darkness. It consists from a chuck on the moving stage, a level for the manipulators and a movable microscope. The bias is supplied to the chuck on which the wafer (or a chip, like in figure 17b) is laying. The front side contacts are made with needles. Test structures, FETs and TLMs were measured using a probecard with four probes with 200 μm pitch.

**Figure 17.** Probestation that was used in IV measurements, a) entire probestation inside the cabinet, b) closeup of a gated diode sample contacted with needles.

The diode connections to the parameter analyzer are shown in figure 18. In the picture the connections for gated diodes are shown. If the diode did not have a gate, SMU4 was not used and the measurement was done with two probes instead of three. The high voltage was supplied to cathode through SMU1. Depending on the measurement type (cathode sweep or gate sweep) the voltage was either sweeped from  $0\,\mathrm{V}$  to  $50/100\,\mathrm{V}$  and back to  $0\,\mathrm{V}$ . The maximum voltage was usually  $50\,\mathrm{V}$  for the gated diodes and for diodes without gate it was  $100\,\mathrm{V}$ . The voltage was set to  $0\,\mathrm{V}$  to anode and to guard ring through SMU2 and SMU3. The gate voltage was varied through SMU4, both positive and negative voltages were used. Current was measured from all four contacts.

CV, TCT and radiation measurements were done at Helsinki Institute of Physics (HIP) Detector Laboratory at Kumpula campus, and the IV results of chips used in those measurements were tested with their setup. Setup consisted from probe station with needles attached to micromanipulators. The largest difference was that current was only measured from the cathode (backside of the wafer) and anode. The guard ring was connected to the ground. The voltage was supplied to the cathode by Keithley 2410 source meter and it was also used to measure the total current. The anode current was measured with Keithley 2410 picoAmpere-meter. [38] For the gated diodes the gate voltage was supplied with PS613 DC power supply (positive voltages only). Measurements done with HIP setup

**Figure 18.** Connections to parameter analyzer in diode IV measurements.

will be mentioned in results, otherwise they are measured with VTT Micronova setup.

## Transfer length method (TLM) measurements

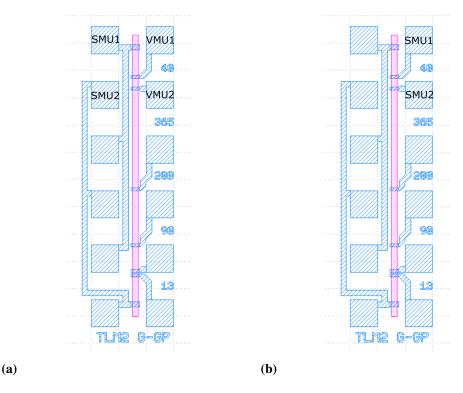

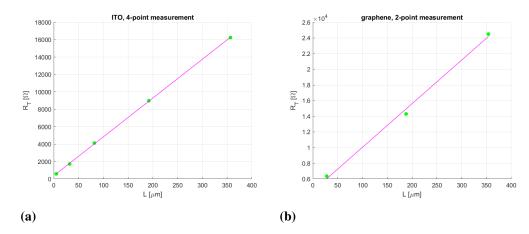

In order to find out the contact resistance between gate material (ITO/graphene) and the contact pad material (Al/CrAu), transfer length method was used for measuring the structure in figure 19. The measurement was done with the same setup as described above, using a four needle probecard with 200 µm pitch. In figure 19a is shown the connections to parameter analyzer in case of four point measurement. During measurement, current was supplied to the pads on the left side of the structure through SMU1 and SMU2 and induced voltage was measured from the right side of the structure (VMU1 and VMU2). After each measurement the probes were moved over next length and the measurement was repeated. In the structure there were five different lengths to measure.

It was not possible to get results with four point measurement from graphene gated TLM structure, and instead the measurement was done as two point measurement. In two point measurement the current was supplied through the same pads from which the voltage was measured, this is shown in figure 19b. The most probable reason for four point measurement not working with graphene as gate material is breaking of graphene at some point of the structure. The width of the gate bar is  $20\,\mu\mathrm{m}$  and it goes on top of the gate pads, as the metal deposition was done before gate material deposition.

**Figure 19.** TLM measurement structures with measurement contacts for a) four point measurement and b) two point measurement. The blue parts are contact pads and the pink bar is gate material.

During measurement the voltage was sweeped through SMU1 from  $0\,\mathrm{V}$  to  $250\,\mathrm{mV}$ , then to  $-250\,\mathrm{mV}$  and back to  $0\,\mathrm{V}$  with  $50\,\mathrm{mV}$  steps. The voltage of SMU2 was set to  $0\,\mathrm{V}$ . Same applies to both four point and two point measurements.

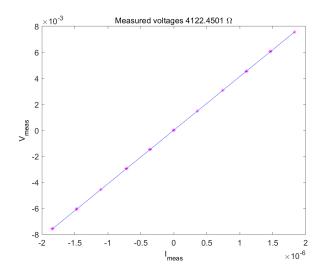

When the measured voltage values are plotted as a function of the supplied current, the line fitted into the data gives the value of resistance during the measurement. That is the total resistance of the system. In the four point measurement the value of the measured voltage is plotted as difference between two measured voltages (VMU2-VMU1). In two point measurement the resistance is calculated from measured voltages from SMUs. An example from measurement data from four point measurement is shown in figure 20. When all different lengths are measured, the resistance values from all of them are used to calculate the contact resistance.

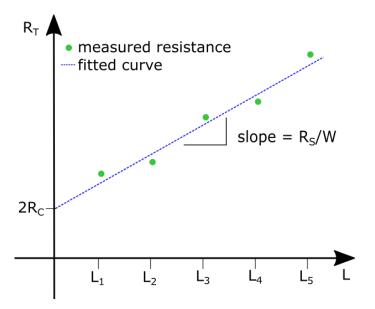

By plotting the total resistances  $R_T$  as function of the length (fig. 21), a line can be fitted into the data. Equation of that line is

$$R_T = \frac{R_S}{W}L + 2R_C, (2)$$

where  $R_S$  is the sheet resistance, W is the width of the TLM bar and  $R_C$  is the contact

Figure 20. Measurement data from TLM four point measurement.

**Figure 21.** Determining  $R_C$  from measurement data. Based on picture in [39].

resistance [39]. From that equation contact and sheet resistances can be solved.

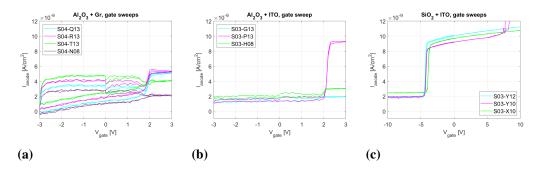

#### **FET measurements**

In order to figure out suitable gate voltages for diode measurements, couple of FETs were measured. The connections for FET measurements are shown in figure 22. During measurement, the source voltage was set to  $0\,\mathrm{V}$  through SMU1. For gate sweeps the drain voltage was set to fixed negative values through SMU3 while the gate was sweeped from minimum value to maximum value (SMU2) and back to minimum value. The used values of drain and gate voltages varied between components. Current was measured through all three SMUs. Figure 22b shows the contact points for probes. At the right bottom corner

there is pad that is not connected to anywhere and there is no SMU marked to it. That pad was just a place for fourth probe of the probe card which was not needed during the measurement.

**Figure 22.** Connections used in FET measurements a) connections to SMUs from the cross sections b) mask design showing the SMU connections.

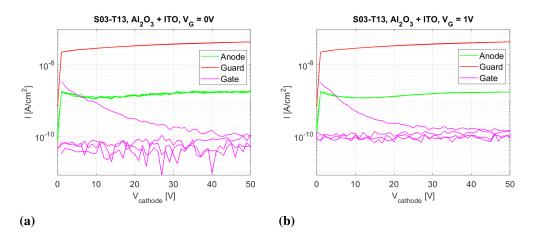

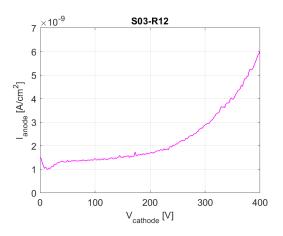

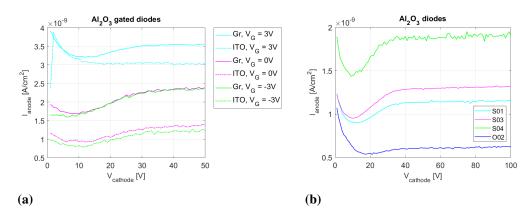

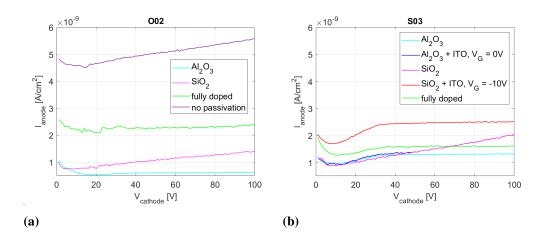

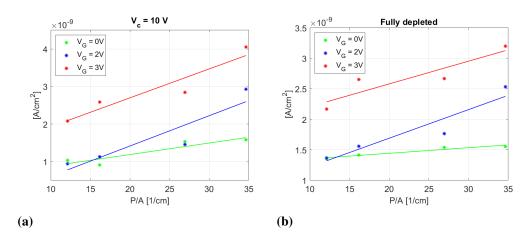

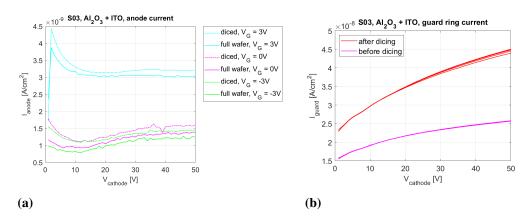

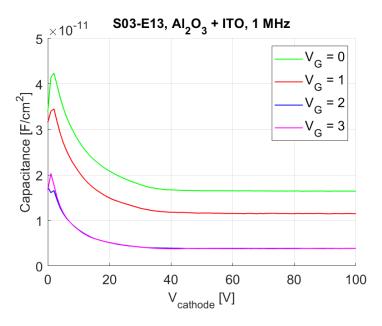

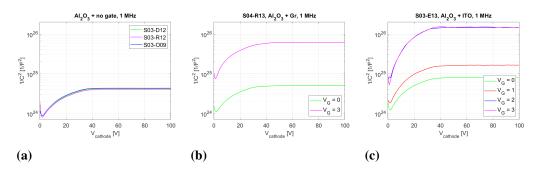

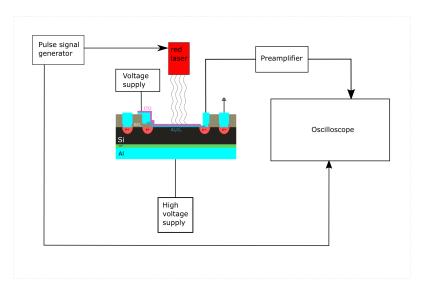

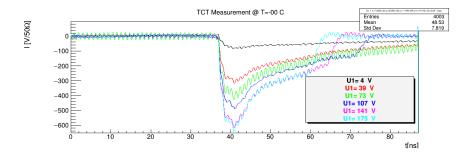

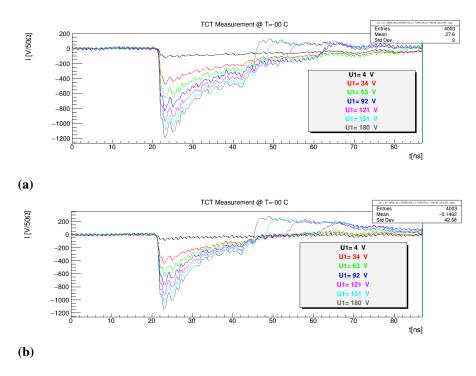

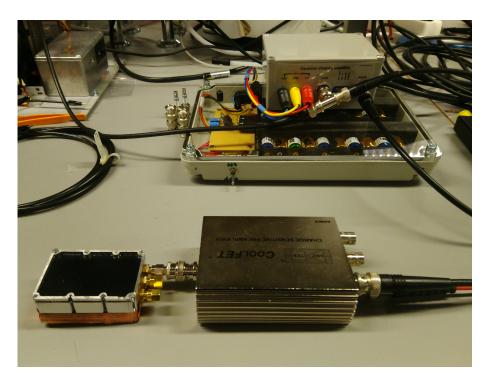

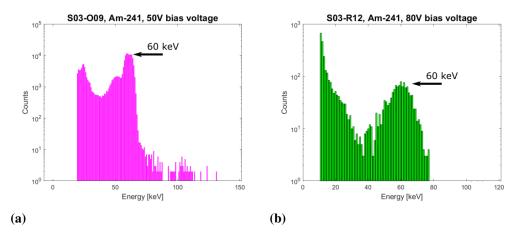

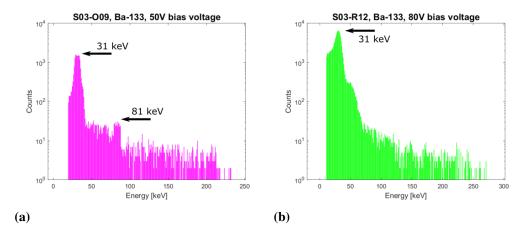

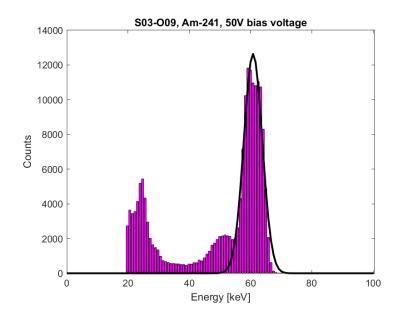

#### Analyzing components of leakage current