### AVALANCHE ROBUSTNESS OF SILICON CARBIDE MOSFETS

Lappeenranta–Lahti University of Technology LUT Electrical engineering, Master's Thesis 14.10.2022 Jimmy Ingman Examiner(s): Prof. Pertti Silventoinen M.Sc. Joni Jormanainen

#### ABSTRACT

Lappeenranta–Lahti University of Technology LUT LUT School of Energy Systems Electrical Engineering

Jimmy Ingman

#### Avalanche Robustness of Silicon Carbide MOSFETs

Master's thesis 14.10.2022 76 pages, 51 figures, 6 tables and 1 appendix Examiner(s): Prof. Pertti Silventoinen M.Sc. Joni Jormanainen

Keywords: Avalanche breakdown, avalanche ruggedness, silicon carbide, power MOSFET, unclamped inductive switching.

This thesis presents a test setup and procedure to investigate the avalanche ruggedness (AR) of silicon carbide metal-oxide-semiconductor field-effect transistors (SiC MOS-FET). This test is also known as the unclamped inductive switching (UIS) test.

The avalanche phenomenon affects the doped body of the MOSFET and its ability to block current in the reverse direction. Whenever a current through an inductance is interrupted fast, an electromagnetic counter force is induced, which consequently builds up high potentials across the switching device. Especially in snubber-less designs where inductive switching is present, the power semiconductor can be exposed to an avalanche event, which may result in device failure. Traditionally, conventional silicon device manufacturers express the single pulse avalanche energy in their datasheets, but for newer SiC MOSFETs, this information is often missing. Therefore, single pulse avalanche energies were determined for the tested devices as part of this work.

The aging aspect of AR testing involves exposing the device under test (DUT) to avalanche energies below the point of irreversible breakdown. In this study, SiC MOSFETs from two different manufacturers were stressed by repeated single-pulse avalanche exposure at a frequency of one hertz and energies slightly below their determined maximum values. The DUTs were electrically characterized and imaged with X-ray and scanning acoustic microscopy throughout the tests to assess the inflicted degradation. Failure analysis of the failed DUTs from the first manufacturer revealed three distinct failure modes, whereas no definite conclusions could be drawn for the DUTs from the second manufacturer. Finally, a complete AR testing and workflow procedure were presented for carrying out the AR test successfully.

The AR test setup and the developed process proved to be valuable in determining the avalanche ruggedness of SiC MOSFETs, as well as a valuable test for supporting the overall reliability evaluation of a power semiconductor device.

#### TIIVISTELMÄ

Lappeenrannan–Lahden teknillinen yliopisto LUT LUT Energiajärjestelmät Sähkötekniikka

Jimmy Ingman

#### Vyöryläpilyöntikestävyys SiC-MOSFET komponentissa

Sähkötekniikan diplomi tutkielma 14.10.2022 76 sivua, 51 kuvaa, 6 taulukkoa ja 1 liite Tarkastaja(t): Prof. Pertti Silventoinen DI. Joni Jormanainen

Avainsanat: Vyöryläpilyönti, vyöryläpilyönti kestävyys, piikarbidi, teho-MOSFET.

Tämä diplomityö käsittelee piikarbidi-MOS-transistorin (SiC MOSFET) vyöryläpilyöntikestävyyden testausta, eli AR-testausta (avalanche ruggedness), ja sitä varten rakennettua testilaitteistoa. Kyseinen testimenetelmä tunnetaan myös nimellä UIStesti (unclamped indutctive switching).

Vyöryläpilyönti koettelee MOS-transistorin virran estokykyä sähkötermisesti. Virtapiirin äkillinen avaus saa aikaan voimakkaan sähkömagneettisen vastavoiman, joka aiheuttaa korkean potentiaa-lieron piikarbidisirun yli. Tämän nopean jännitepiikin energia saattaa johtaa komponentin hajoami-seen. Perinteisesti valmistajat ilmoittavat kuinka suurienergiaisen piikin eli läpilyöntienergian kom-ponentti kestää, mutta uudemmille piikarbidi-MOS-transistoreille tätä tietoa harvemmin annetaan. Tämän vuoksi maksimaaliset läpilyöntienergiat selvitettiin testattaville komponenteille työn osana.

Eritoten diplomityössä haluttiin tutkia testattavien komponenttien kestävyyttä useamman peräkkäisen vyöryläpilyönnin tapauksessa; tätäkään tietoa ei piikarbidi-MOStransistoreille ole saatavilla. Työssä tähän tarkoitukseen kehitetyssä testissä läpilyöntienergia asetettiin hieman alle selvitetyn maksimaalisen arvon, jotta testattavia komponentteja rasitettaisiin mahdollisimman paljon, mutta kuitenkin siten että ne kestäisivät useamman sadan pulssin sarjan yhden hertsin taajuudella. Ennen testiä ja sen jälkeen komponentit karakterisoitiin sähköisesti sekä kuvattiin röntgenillä ja ultraäänellä, jotta rasituksen mahdollisia vaikutuksia voitaisiin arvioida.

Yllä käsitellyt toimenpiteet kostettiin prosessiksi, jonka mukaisesti testattiin kahta eri valmistajan kaupallisesti saatavilla olevaa piikarbidi-MOS-transistoria. Toisen valmistajan komponenttien havaittiin vikaantuvan kolmella eri tavalla, kun taas toisesta oli vaikeampi tehdä johtopäätöksiä. Testilaitteisto ja kehitetty prosessi osoittautuivat toimiviksi vyöryläpilyöntikestävyyden selvittämiseksi.

#### ACKNOWLEDGEMENTS

I want to thank all the people who have contributed in one way or another to completing this thesis. Special thanks to my manager from ABB Oy, Drives M.Sc. Janne Davidsainen, for the exciting opportunity. First of all, I would like to thank Professor Pertti Silventoinen, who acted as my supervisor during this thesis, for the good discussions, valuable advice on technical and scientific expression related questions, and for the constructive, encouraging, and insightful feedback I received during this work. I also want to express my special thanks to M.Sc. Joni Jormanainen, who served as the thesis supervisor, for his motivating and tremendous guidance during this work. Without your assistance and guidance, this work most likely would not have been completed. I also thank the people at ABB CRC in Switzerland for their time and advice regarding this work.

Furthermore, I want to thank M.Sc. Aleksi Vulli for his support and help during the years of my studies. You have been a superhero.

Finally, I want to thank my family and friends for the support needed during these years of my studies.

Thank you, thank you, thank you.

Helsinki, 6.10.2022

Jimmy Ingman

## SYMBOLS AND ABBREVIATIONS

## Greek characters

$\epsilon_{\rm S}$  relative dielectric constant

# Roman characters

| C    | capacitance       | [F]                       |

|------|-------------------|---------------------------|

| i, I | current           | [A]                       |

| f    | frenquency        | [Hz]                      |

| R    | resistance        | [Ohm]                     |

| Т    | temperature       | $[{}^{\underline{0}}C,K]$ |

| t    | time              | $[\mathbf{S}]$            |

| u, U | voltage           | [V]                       |

| L    | inductance        | [H]                       |

| Р    | power             | [W]                       |

| q    | elementary charge | [C]                       |

|      |                   |                           |

# Symbols

| D             | drain of MOSFET                 |  |

|---------------|---------------------------------|--|

| E             | electric field                  |  |

| $E_{\rm AV}$  | avalanche energy                |  |

| $E_{\rm C}$   | critical electric field         |  |

| G             | gate of MOSFET                  |  |

| $I_{\rm D}$   | drain current                   |  |

| $I_{\rm DS}$  | drain to source current         |  |

| $I_{\rm DSS}$ | drain to source leakage current |  |

| $I_{ m GS}$   | gate to source current          |  |

| $I_{ m GSS}$       | gate to source leakage current           |  |  |

|--------------------|------------------------------------------|--|--|

| $N_{\rm D}$        | doping concentration in the drift region |  |  |

| $R_{\rm A}$        | MOSFET accumulation region resistance    |  |  |

| $R_{\rm D}$        | MOSFET drift region resistance           |  |  |

| $R_{\rm DSon}$     | MOSFET drain source on-state resistance  |  |  |

| $R_{\rm S}$        | MOSFET source resistance                 |  |  |

| $R_{\rm sub}$      | MOSFET substrate resistance              |  |  |

| S                  | source of MOSFET                         |  |  |

| $T_{ m J}$         | junction temperature                     |  |  |

| $t_{\rm AV}$       | time in avalanche                        |  |  |

| $t_{\rm off}$      | signal off-time                          |  |  |

| ton                | signal on time                           |  |  |

| $V_{\rm BR(eff)}$  | effective avalanche breakdown voltage    |  |  |

| $V_{\rm DB}$       | breakdown voltage                        |  |  |

| $V_{\rm DC}$       | DC-Voltage                               |  |  |

| $V_{\rm DD}$       | supply voltage                           |  |  |

| $V_{\rm DS}$       | drain-source voltage                     |  |  |

| $V_{ m GS}$        | gate-source voltage                      |  |  |

| $V_{ m GSth}$      | gate-source threshold voltage            |  |  |

| $V_{ m in}$        | input voltage                            |  |  |

| $V_{\mathrm{out}}$ | output voltage                           |  |  |

| $V_{ m th}$        | MOSFET threshold voltage                 |  |  |

# Abbreviations

ABBAsea Brown BoveriACAlternating CurrentARAvalanche RuggednessEMFElectromagnetic forceDCDirect Current

| DUT    | Device Under Test                                 |  |  |

|--------|---------------------------------------------------|--|--|

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |  |  |

| PCB    | Printed Circuit Board                             |  |  |

| PCBA   | Printed Circuit Board Assembly                    |  |  |

| RMS    | Root-Mean-Square                                  |  |  |

| SAM    | Scanning Acoustic Microscopy                      |  |  |

| SC     | Short Circuit                                     |  |  |

| Si     | Silicon                                           |  |  |

| SiC    | Silicon Carbide                                   |  |  |

| SOA    | Safe Operating Area                               |  |  |

| ТО     | Transistor Outline                                |  |  |

| UIS    | Unclamped Inductive Switching                     |  |  |

| VD     | Vertically Diffused                               |  |  |

| WBG    | Wide bandgap                                      |  |  |

# Contents

| A        | bstra | $\operatorname{ct}$                    | i   |

|----------|-------|----------------------------------------|-----|

| A        | ckno  | wledgements                            | iii |

| Sy       | mbo   | ls and abbreviations                   | iv  |

| 1        | Intr  | oduction                               | 1   |

| <b>2</b> | Silie | con carbide power MOSFET               | 3   |

|          | 2.1   | Structure                              | 4   |

|          | 2.2   | Operation                              | 6   |

|          |       | 2.2.1 On-state                         | 6   |

|          |       | 2.2.2 Switching characteristics        | 8   |

|          | 2.3   | Avalanche breakdown                    | 15  |

| 3        | Ava   | lanche ruggedness test                 | 18  |

|          | 3.1   | Test system                            | 18  |

|          | 3.2   | Test description                       | 18  |

|          | 3.3   | Performing an avalanche event          | 20  |

|          | 3.4   | Measurements during an avalanche event | 21  |

|          | 3.5   | Test bench                             | 22  |

| 4        | Ava   | lanche ruggedness test procedure       | 26  |

|          | 4.1   | Implemented test procedure             | 26  |

|          | 4.2   | Setting the aging parameter values     | 29  |

| <b>5</b> | Ana   | lysis and results                      | 31  |

|          | 5.1   | Cree C2M1000170                        | 31  |

|          | 5.2   | Summary of the Cree C2M1000170 devices | 48  |

|          | 5.3   | Rohm SCT2H12NZ                         | 49  |

|          | 5.4   | Summary of the Rohm SCT2H12NZ devices  | 59  |

| 6        | Dis   | cussion                                | 60  |

| 7 Conclusions                                                    | 62 |

|------------------------------------------------------------------|----|

| References                                                       | 66 |

| Appendices                                                       | 67 |

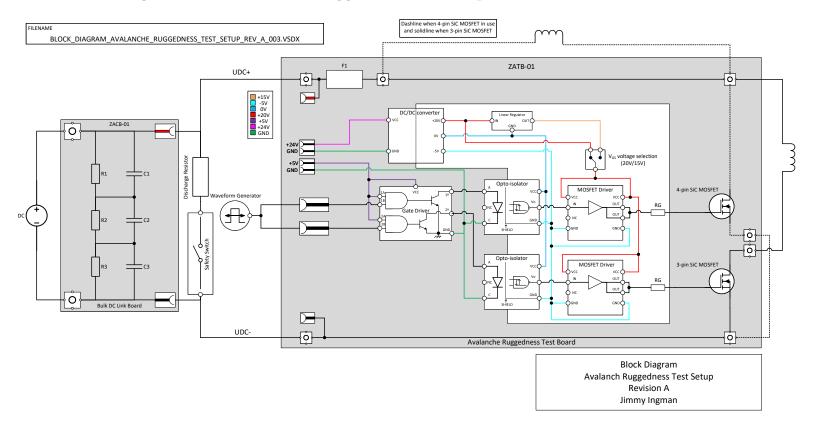

| Appendix 1: Block diagram of the avalanche ruggedness test setup | 67 |

## 1 Introduction

Over the past decade, silicon carbide (SiC) power Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET) manufacturing technology has experienced rapid technological development and is nowadays a commercial reality and available from numerous manufacturers with various ratings. SiC power MOSFETs are nowadays in the spotlight and are one of the most typical SiC devices available in the market.Compared to conventional silicon-based MOSFETs, silicon carbide MOSFETs delivers a higher switching frequency capability, lower on-state resistance, and better off-state performance due to a small leakage current (Elasser & Chow, 2002; Hull et al., 2011).

Before SiC power MOSFETs can be implemented in power systems on a larger scale to acquire the advantages previously mentioned, it is essential to characterize these devices in terms of their robustness and reliability. Unclamped inductive switching (UIS) and short circuit (SC) tests are widely used in the power electronics industry to determine the limits of the device's safe operating area (SOA) (Fayyaz et al., 2017). This thesis will focus on the first testing methodology, unclamped inductive switching, also known as avalanche ruggedness (AR).

Power MOSFETs are widely used in high switching frequency applications where inductive loads are present, for example, motor drive applications and flyback converters. These applications require the device to withstand a particular duration of avalanche breakdown. Power MOSFET encounters an avalanche breakdown between the drain and source at the cut-off transient. This fast current interruption of an unclamped inductive load produces a back electromagnetic force dissipating into the device and the harsh switching transient could damage the device or cause it to fail. AR is an essential feature for a power device which defines its capability to dissipate avalanche energy  $E_{\rm AV}$  without catastrophic device failure. This also enables the design to be snubber less, thus reducing the cost by a smaller number of components and decreasing the converter size. (Fayyaz et al., 2017)

The goal of this thesis is to provide a test setup to compare the repetitive AR of SiC power MOSFETs. A testing procedure to investigate the effects of the AR test as well as how to evaluate the aging parameters are also proposed in this thesis. Finally, SiC MOSFETs of two different suppliers are tested and benchmarked in an effort to verify the proposed testing scheme as well as to investigate usefulness of the AR test in terms of component reliability testing. The usefulness of the AR test is further address through failure analysis of a few selected failed samples. However, determination of the true root cause of the failure is beyond the scope of this thesis.

In Chapter 2, the general aspects of SiC semiconductors are discussed, and a brief comparison between the SiC and the silicon-based power MOSFET is presented. An introduction to different SiC power MOSFET structures is also provided followed by an overview of the switching characteristics of the SiC MOSFET related to the AR test. Chapter 3 presents the designed AR test setup and the measurements obtained during an avalanche event. In Chapter 4, the implemented testing procedure is presented as well as how the aging parameter values for the device under test (DUT) are discovered. In Chapter 5, the analysis of the measurement results of two different suppliers tested in the AR test are examined in detail and the final findings are presented and discussed in Chapter 6. Finally, the conclusions of this thesis are presented in Chapter 7 as well as some future work. The block diagram of the AR test setup designed for this thesis is given in the Appendix.

## 2 Silicon carbide power MOSFET

The power MOSFET is a semiconductor device widely used for high power conversion in electronic devices. MOSFETs are used in various applications such as power supplies, consumer electronics, automotive electronics, and electric power converters (Witczak et al., 2021). Power MOSFET devices have long been critical components in power converters due to their high switching frequency characteristics (Elasser & Chow, 2002). The leading semiconductor manufacturing material for the past two decades has been silicon (Si). Si-based power devices have approached their physical performance limitations, leading to new materials being investigated (She et al., 2017). Lately, new semiconductor counterpart materials such as silicon carbide (SiC) have been introduced to the power device markets.

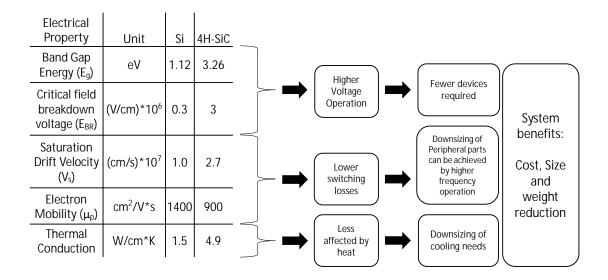

The SiC technology enables manufacturing of power semiconductor devices with significantly increased voltage capabilities ( $\geq 0.6 - 3.3 \ kV$ ) compared to the conventional silicon-based technology ( $\leq 1 \ kV$ ) (ROHM, 2020*b*, p. 11). The essential properties of SiC-based power devices originate from their wide band gap (WBG) semiconductor materials and allows for low-on resistance, which reduces switching losses and permits higher switching frequencies than with Si-based power devices (She et al., 2017). SiC offers ten times higher electric-field breakdown capability and three times higher thermal conductivity, allowing the SiC devices to operate at higher power densities and temperatures than the counterpart Si devices (Elasser & Chow, 2002; She et al., 2017). The essential characteristics of silicon compared to silicon carbide are summarized in Figure 1. The benefits provided by SiC properties can be translated into system-level advantages by reducing the system size, weight, and cost over systems using Si devices (Elasser & Chow, 2002; She et al., 2017).

Figure 1: Semiconductor material properties (ROHM, 2020a, p. 5).

The following chapters examine the structure and operation principle of the SiCbased power MOSFET.

#### 2.1 Structure

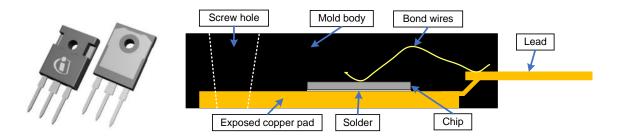

A silicon carbide MOSFET structure is very similar to its counterpart Si MOSFET. Power MOSFETs are typically packaged discretely, meaning that only one semiconductor chip is assembled inside a package. The most dominating packaging method for power MOSFETs has been the transistor outline (TO) family, of which the most typical standardized transistor packages are the TO-220 and TO-247. These packages consist of three leads, also called legs or pins. Two of the leads are attached to different areas of the power silicon chip via bond wires, commonly made of aluminum or copper. The MOSFET chip is soldered straight to a solid mounting surface of copper, which is a part of the last lead. All the pieces are fixed by a transfer mold, leaving only the legs and, for some devices, the backplate bare. In applications, the MOSFET legs are soldered to the printed circuit board (PCB), where the backplate of copper is typically attached to an external heat sink for greater cooling performance. A simplified drawing of a TO-247 packaged MOSFET is shown in Figure 2. (Lutz et al., 2018, p. 433)

Figure 2: Power MOSFET packing principle. TO-247 package on the left-hand side (Lutz et al., 2018, p. 433).

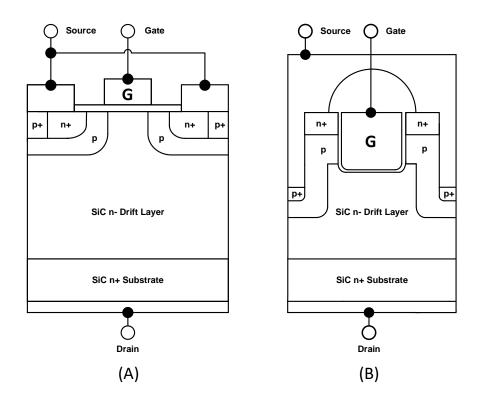

One of the typical die structures of a power MOSFET is the Vertical Diffused (VD) MOSFET, also known as the planar structure. The device consists of three different terminals: Gate (G), Drain (D), and Source (S). The gate and source terminals are located on the structure's top side. The two terminals are connected to the legs of the package via the internal bonding wires. The drain terminal is found on the bottom side of the structure and is attached to the device's backplate. The word "Vertical" represents the current flowing vertically from the drain terminal to the source terminal when a positive voltage is applied to the gate. The "Diffused" refers to the manufacturing process called diffusing. With this technique, individual cells are formed consisting of p-wells and diffused n+ areas of the semiconductor, which allows the functionality of the device channel (Lutz et al., 2018, pp. 344-345).

Another typical die structure of a power MOSFET is the U-MOSFET, also known as the trench-gate structure. The main difference in the structure comes from how the gate in the cells is constructed, also termed gate build-up. The gate trench stretches from the upper surface of the structure through the n+ source and p base regions into the n- drift region (Baliga, 2018, p. 289). Both structures are illustrated in Figure 3, where (A) represents the planar structure, and (B) the trench-gate structure.

Figure 3: Regular SiC MOSFET structures (A) planar and (B) trench.

As seen in Figure 3 above, the difference between these two structures comes mainly from the gate build-up. The essential difference is the amount of on-resistance during forward conduction. The on-resistances affect the structures' different current flow paths and will be discussed in the next section.

## 2.2 Operation

#### 2.2.1 On-state

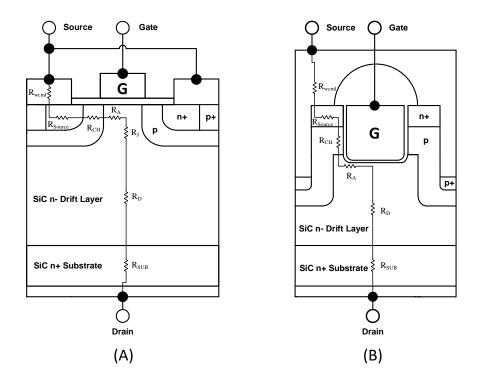

The power MOSFET is turned conductive with a positive gate-source voltage  $V_{\rm GS}$ . As the voltage is applied between the gate and the source, an inversion layer channel at the surface of the p base region under the gate electrode starts to form. When the applied gate voltage  $V_{\rm GS}$  surpasses the gate threshold voltage  $V_{\rm GSth}$ , the inversion layer channel extends from the n+ source region to the n- drift region. It forms a conduction path between the drain and the source terminals, and if a positive drain-source voltage  $V_{\rm DS}$ is applied, the current flows vertically between the drain and source via this inversion layer channel. If the gate-source voltage  $V_{\rm GS}$  drops below the gate threshold voltage  $V_{\rm GSth}$ , the channel is closed, and the current flow is shut. (Baliga, 2010, pp. 23-24) At the start of the conduction, the current passes several resistive components collectively called on-state resistance  $R_{\text{DSon}}$  (Baliga, 2011, p. 239). The planar structure's on-state resistance is divided into seven different resistances. Six of them are related to the chip: the n+ source diffusion resistance  $R_{\text{Source}}$ , channel resistance  $R_{\text{ch}}$ , accumulation-layer resistance  $R_{\text{A}}$ , "JFET" component-resistance  $R_{\text{J}}$ , drift-resistance  $R_{\text{D}}$ , and the n+ substrate resistance  $R_{\text{sub}}$ . The seventh resistance  $R_{\text{wcml}}$  is related to the packing factors. This resistance  $R_{\text{mcml}}$  combines the sum of bond wire resistance  $R_{\text{BW}}$ , the die attach solder resistance  $R_{\text{Die}}$ , and the contact resistance  $R_{\text{C}}$  between the metallization-to-chip (Dusmez et al., 2016). The total on-state resistance for a planar type MOSFET is the sum of the individual resistances of each layer and region and can be calculated as (Dusmez et al., 2016):

$$R_{\rm DSon} = R_{\rm wcml} + R_{\rm Source} + R_{\rm ch} + R_{\rm A} + R_{\rm J} + R_{\rm D} + R_{\rm sub}.$$

(1)

It is also worth mentioning that for high power MOSFETs and typically for high voltage devices, the significant contribution of the on-state resistance is the parasitically formed JFET region resistance  $R_{\rm J}$  and the drift region resistance  $R_{\rm D}$ . The rest of the layer and channel resistance are relatively small, and the  $R_{\rm wcml}$  is generally negligible for such high voltage devices (Dusmez et al., 2016).

A cross-section of both structures is illustrated in Figure 4, where (A) represents the planar structure, and (B) the trench-gate structure.

Figure 4: Regular SiC MOSFET structures (A) planar and (B) trench.

As seen in Figure 4 above, almost the same internal resistances apply to both structures. The major difference is that the JFET region is eliminated for the trench structure. The trench extends from the upper surface of the n+ source beyond the bottom of the p base region into the n- drift layer and forms a shorter channel between these two layers. Thus, the total on-state resistance is lower for a trench-gate structured MOSFET (Baliga, 2010, p. 66). The total on-state resistance for trench type MOSFET is calculated as:

$$R_{\rm DSon} = R_{\rm wcml} + R_{\rm Source} + R_{\rm ch} + R_{\rm A} + R_{\rm D} + R_{\rm sub}.$$

(2)

#### 2.2.2 Switching characteristics

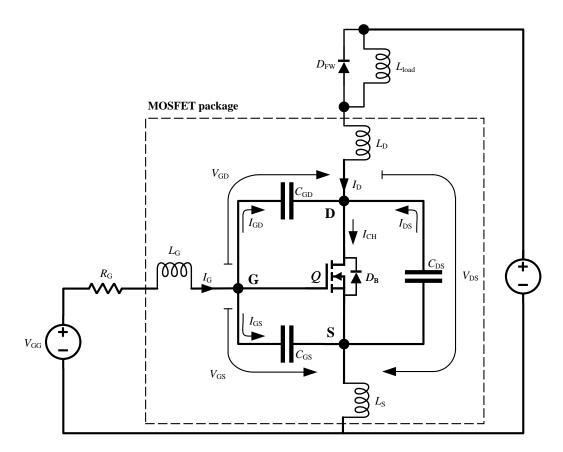

In order to study the switching characteristics of a power MOSFET, it is necessary to know the parasitic elements of the device. One of the parasitic elements are the parasitic capacitances that originate from the electric conductors with different potentials close to each other. This potential difference causes a charge between them and forms unwanted capacitors. For the power MOSFET structure, three different capacitances exist between the terminals and are commonly divided into the following capacitances: Input capacitance  $C_{\rm GS}$  between the gate and the source terminals, output capacitance  $C_{\rm DS}$  between the drain and the source terminals, and the Miller capacitance  $C_{\rm GD}$  between the gate and the drain terminals (Baliga, 2018, pp. 413-414).

The parasitic inductances are the other parasitic elements that affect the switching of a power MOSFET. The parasitic inductances originate from the internal electrical conductors of the device and are divided according to the device terminals: Gate inductance  $L_{\rm G}$ , drain inductance  $L_{\rm D}$ , and the source inductance  $L_{\rm S}$ . (Qin et al., 2018)

These parasitic elements affect the switching behavior of the power MOSFET ether in their own way or combined with each other. The gate inductance  $L_{\rm G}$  combined with the input capacitor  $C_{\rm GS}$  can induce spurious oscillations in the gate voltage  $V_{\rm GS}$ (Locorotondo et al., 2019). This again affects the device turn-on operation and can cause oscillations in the drain to the source voltage  $V_{\rm DS}$ . This oscillation can be avoided by placing the device close to the gate drive circuit and minimizing the drive loop inductance of the circuit. The effect of this parameter is usually limited and is the least severe of the three primary sources of parasitic inductances. The drain inductance  $L_{\rm D}$  resonating with the output capacitance  $C_{\rm DS}$  generates a more significant effect on the switching transient of the device. This causes the oscillation to be coupled into the Miller capacitance  $C_{\rm GD}$ , which generates oscillation in the gate loop and causes ringing in the device drain voltage  $V_{\rm DS}$ , gate voltage  $V_{\rm GS}$ , and drain current  $I_{\rm D}$ . The most significant component impacting the switching transients of the MOSFET is the parasitic inductance of the source  $L_{\rm S}$ . During the switching transient of the device, the inductance  $L_{\rm S}$  work as negative feedback from the switching loop to the gate driver loop. As the drain current changes during switching, the voltage over  $L_{\rm S}$  counteracts the gate voltage and, at the same instant, slows down the current flow of the device and yields higher switching losses during turn-on and turn-off of the device. (Chen et al., 2010)

The switching behavior of a SiC MOSFET can be examined with the help of a clamped inductive circuit, as shown in Figure 5. The circuit consists of two voltage sources. One of them is the supply voltage  $V_{\rm DC}$  which provides a constant voltage to the main circuit. The other is the voltage source  $V_{\rm GG}$  for the gate circuit and provides a step voltage via the external gate resistor  $R_{\rm G}$  to the device gate pin. The

circuit also includes a free-wheeling diode  $D_{\rm FW}$  connected in parallel with the load inductor  $L_{\rm load}$ . When the MOSFET is not conducting, the load current is clamped via this free-wheeling diode. The Q represents the SiC MOSFET.  $L_{\rm G}$ ,  $L_{\rm D}$ , and  $L_{\rm S}$ are the parasitic inductances. These inductances originate from contact leads between the device and the circuit, where the  $L_{\rm G}$  is the inductance between the gate pin and the gate drive circuit.  $L_{\rm D}$  is the inductance between the main circuit and the drain pin.  $L_{\rm S}$  is the inductance between the common ground and the source pin. The  $C_{\rm GD}$ ,  $C_{\rm GS}$ , and  $C_{\rm DS}$  are the gate-drain, gate-source, and drain-source parasitic capacitances originating from the MOSFET structure.

Figure 5: Power MOSFET in an ideal clamped inductive circuit.

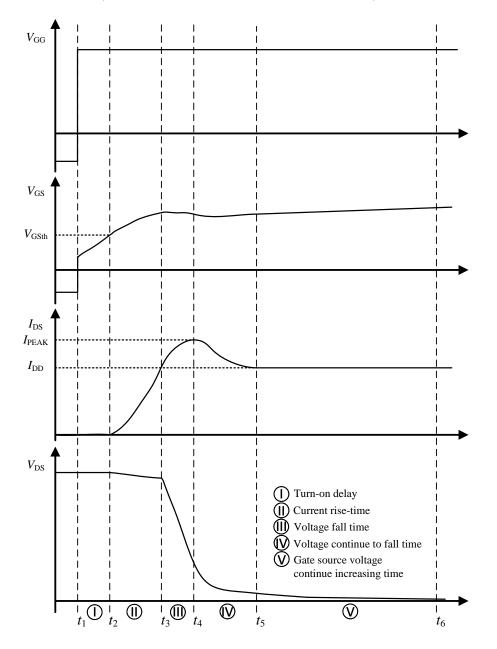

The turn-on period can be divided into five stages, as shown in Figure 6. The first stage is the turn-on delay for the MOSFET  $(t_1-t_2)$ . At time  $t_1$ , the gate signal  $V_{\text{GG}}$ increases from a negative to a positive voltage, and the gate-source voltage  $V_{\text{GS}}$  rises from a negative to a positive threshold voltage  $V_{\text{GSth}}$ . A gate current  $I_{\text{G}}$  starts to flow and charges up the input capacitance  $C_{\text{iss}} = C_{\text{GD}} + C_{\text{GS}}$  via the resistance  $R_{\text{G}}$ . During this stage,  $V_{\rm GS}$  raises according to the following exponential function:

$$V_{\rm GS} = V_{\rm GG} (1 - e^{\frac{t}{t_{\rm iss}}}), \tag{3}$$

where the time constant  $t_{\rm iss} = R_{\rm G}C_{\rm iss}$ . Under this turn-on delay stage  $(t_1-t_2)$ , the MOSFET is still in off-state, zero drain current is conducted through the device's channel, and the drain to source voltage  $V_{\rm DS}$  remains unchanged and is equal to the supply voltage  $V_{\rm DC}$ . (Cittanti et al., 2017; Zhang et al., 2018)

Figure 6: Waveforms of a SiC MOSFET during turn-on transient. Adapted from (Zhang et al., 2018).

The second stage is the current rise-time  $(t_2-t_3)$ . At time  $t_2$ , the  $V_{\text{GS}}$  exceed the  $V_{\text{GSth}}$  level, and the current from the load starts to flow through the MOSFETs channel. During this stage, the MOSFET works as a voltage-controlled current source, and the current rises according to the following equation (Cittanti et al., 2017; Zhang et al., 2018):

$$I_{\rm D} = g_{\rm fs} (V_{\rm GS}(t) - V_{\rm GSth}), \tag{4}$$

whereby the  $g_{\rm fs}$  is the transconductance of the MOSFET (Zhang et al., 2018; Cittanti et al., 2017).

From Figure 6, it can be obtained that a slight fluctuation occurs in both the  $V_{\rm GS}$ and  $V_{\rm DS}$ . This is due to the parasitic elements in the MOSFET. The fluctuation in the  $V_{\rm GS}$  is caused mainly by the injected charge into the miller capacitance  $C_{\rm GD}$ , but the two other parasitic capacitances  $C_{\rm GS}$  and  $C_{\rm DS}$ , also change in value. The decline in the  $V_{\rm DS}$  is due to the parasitic inductance in the MOSFET and can be obtained by the following equation (Zhang et al., 2018):

$$V_{\rm DS}(t) = V_{\rm DC} - (L_{\rm S} + L_{\rm D})^{\frac{dI_{\rm D}(t)}{dt}},\tag{5}$$

whereby the current rate of change is given by:

$$\frac{dI_{\rm D}(t)}{dt} = g_{\rm fs} \frac{V_{\rm GS}(t) - V_{\rm GSth}}{t_{\rm iss}}.$$

(6)

The third stage is the voltage fall time  $(t_3-t_4)$ . At time  $t_3$ , the load current has been fully transferred from the free-wheeling diode,  $D_{\rm FW}$ , to the MOSFET. The energy storage in the parasitic capacitance  $C_{\rm DS}$  of the MOSFET starts to discharge itself via the MOSFET channel as in the following equation (Cittanti et al., 2017):

$$I_{\rm DS}(t) = -C_{\rm DS} - \frac{dV_{\rm DS}(t)}{dt},\tag{7}$$

and the peak current  $I_{\text{PEAK}}$  conducted through the device channel is the sum of the three different currents (Cittanti et al., 2017):

$$I_{\rm PEAK} = I_{\rm DD} + I_{\rm GD} + I_{\rm DS},\tag{8}$$

when the current surpasses the steady-state current  $I_{\text{DD}}$  level and continues to rise, the  $V_{\text{DS}}$  start to decline with a slope according to the following equation:

$$\frac{dV_{\rm DS}}{dt} = -\frac{dV_{\rm GD}}{dt} = -\frac{I_{\rm G}(t)}{C_{\rm GD}},\tag{9}$$

where the gate to drain voltage  $V_{\text{GD}}$  is the voltage of the capacitance  $C_{\text{GD}}$ . During this voltage fall time stage  $(t_3-t_4)$ , the MOSFET operates in the active region, and the peak current  $I_{\text{PEAK}}$  flowing through the device is reached at the end of this stage  $(t_4)$ .

During the fourth stage,  $(t_4-t_5)$ , the voltage continues to fall. At time  $t_4$ , the peak current  $I_{\text{PEAK}}$  is reached and starts to level off to the steady-state current level  $I_{\text{DD}}$ . The  $V_{\text{DS}}$  continue to decrease, and when  $V_{\text{DS}}$  is lower than  $V_{\text{GS}}$ , the operation of the MOSFET shifts from active to the ohmic region driving the device to function as a resistor rather than a voltage-controlled current source (Zhang et al., 2018). The  $V_{\text{DS}}$ decline with a slope according to Equation 9, where the gate driving current  $I_{\text{G}}$  is defined as in the following equation (Zhang et al., 2018):

$$I_G = \frac{V_{\rm GG} - V_{\rm GS}}{R_{\rm G}}.$$

(10)

In the fifth and final stage of the turn-on process of the MOSFET  $(t_5-t_6)$  the  $V_{\rm GS}$  continue to increase according to Equation 3. The rate of change in the slop is driven by the time constant  $t_{\rm iss} = R_{\rm G}C_{\rm iss}$ , and at the end of this stage  $(t_6)$ , the parasitic capacitance  $C_{\rm GD}$  has been completely charged, the gate to source voltage  $V_{\rm GS}$  is leveled to gate driver voltage  $V_{\rm GG}$ , and the MOSFET is now turned on and works in a steady state. (Zhang et al., 2018)

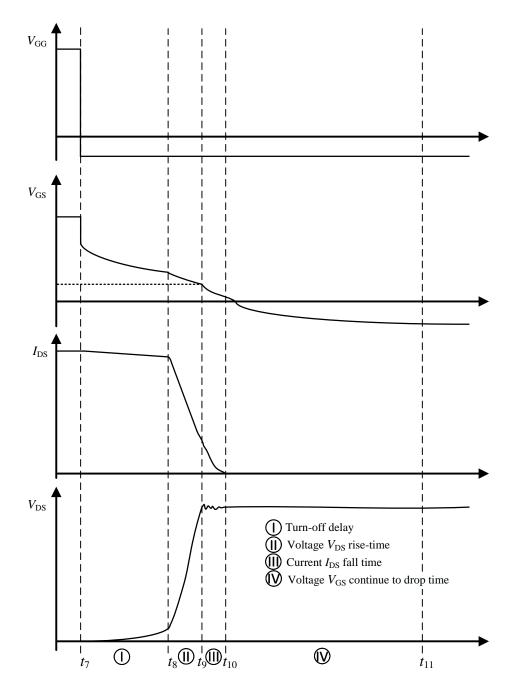

Figure 7: Waveforms of a SiC MOSFET during turn-off transient. Adapted from (Zhang et al., 2018).

The MOSFET turn-off process is similar to the turn-on process and can be divided into four stages, as shown in Figure 7. The first stage is the turn-off delay time ( $t_7$  $t_8$ ). At time  $t_7$ , the gate signal  $V_{\rm GG}$  is shifted instantaneously from positive to a negative voltage. The driving loop discharges the input capacitance  $C_{\rm iss}$  through the gate resistor  $R_{\rm G}$  and  $L_{\rm S}$ , and the gate voltage  $V_{\rm GS}$  drops slightly and starts to decline exponentially, according to Equation 3. During this stage, the gate current  $I_{\rm G}$  can be defined as follows (Zhang et al., 2018):

$$I_{\rm G} = (C_{\rm GS} - (C_{\rm GD}) \frac{dV_{\rm GS}}{dt}.$$

(11)

From Figure 7, it can be noticed that the drain to source voltage  $V_{\text{DS}}$  starts to increase and is mainly driven by the increasing resistance in the device channel. During this stage  $(t_7-t_8)$ , the MOSFET works in the ohmic region.

In the second stage,  $(t_8-t_9)$ , termed voltage rise time stage, the  $V_{\rm DS}$  voltage rises and at time  $t_8$ , the MOSFET transfers from the ohmic region to the active region. The  $V_{\rm GS}$  continues to decrease, and at the end of this stage, the  $V_{\rm GS}$  hits the threshold level  $V_{\rm GSth}$ . The decline of the  $V_{\rm GS}$  relies on the Miller effect and is mainly driven by the discharge of the Miller capacitance  $C_{\rm GD}$ . The drain current  $I_{\rm DS}$  fall rapidly, whereas the drain to source voltage  $V_{\rm DS}$  rises sharply and levels off to the supply voltage  $V_{\rm DC}$ . (Zhang et al., 2018)

In the third stage,  $(t_9-t_{10})$ , is the drain current fall time stage. At time  $t_9$ , the  $V_{\rm GS}$  continue to decline and surpass the threshold voltage  $V_{\rm GSth}$  level, whereby the input capacitance  $C_{\rm iss}$  has been fully discharged. A slight overshoot is noticed in the  $V_{\rm DS}$  due to the free-wheeling diode becoming forward-biased, whereby the load current starts to transfer from the MOSFETs channel to the diode. At the end of this stage  $(t_{10})$ , the drain current reaches zero, and the  $V_{\rm DS}$  continue to be equal to the supply voltage  $V_{\rm DC}$ . (Zhang et al., 2018)

In the fourth and last stage,  $(t_{10}-t_{11})$ , of the turn-off process, the  $V_{\rm GS}$  continue to drop and at time  $t_{10}$ , the  $V_{\rm GS}$  decrease to the negative voltage applied to the MOSFETs gate. The load current is conducted through the free-wheeling diode, and the drain current  $I_{\rm D}$  is equal to zero. The  $V_{\rm DS}$  equals to the supply voltage  $V_{\rm DC}$ , and the MOSFET operates in the cutoff region. (Zhang et al., 2018)

#### 2.3 Avalanche breakdown

Power semiconductor devices such as SiC MOSFETs are designed to withstand high voltages and low drain leakage current during the OFF state of the device. The avalanche breakdown (AR) phenomenon relies on the distribution of the electric field (E) inside the structure of the device. During the development of the desired device, doping of the n- drift layer is carefully selected to acquire the preferred breakdown voltage class. The equations defining the breakdown voltage  $V_{\rm BD}$  for non-fully n depleted region structures can be defined as the following Equation (Baliga, 2010, p. 7):

$$V_{\rm BD} = \frac{\varepsilon_{\rm S} E_{\rm C}^2}{2qN_{\rm D}},\tag{12}$$

where  $\varepsilon_{\rm S}$  is the dielectric constant for the semiconductor material,  $E_{\rm C}$  is the critical electric field for the breakdown of the semiconductor material, q is the charge of an electron, and  $N_{\rm D}$  is the doping of the n type drift region.

The risk of an avalanche phenomenon occurs, for instance, when a current through an inductance is interrupted. This reserved energy in the inductance will build up a counter electromagnetic force (EMF) which induces a high potential across the switching device. The induced potential difference occasionally exceeds the device's rated breakdown voltage  $V_{\text{DSmax}}$ , which produces a high electric field across the reversed biased p-n junction. The strong electric field causes mobile carriers with sufficient energy to collide with lattice atoms, resulting in the generation of electron-hole pairs. This is correspondingly known as impact ionization. The electron-hole pairs induced due to impact ionization result in the generation of additional electrons and hole pairs. Practically the impact ionization is a multiplicative phenomenon producing a continuous flow of electrons via the depletion region, which results in a significant flow of current through the device drain and source. Since the device cannot withstand the use of higher voltages due to the rapid increase in current, the device is considered to be subjected to an avalanche breakdown. Therefore, the avalanche breakdown limits the maximum operating voltage of the semiconductor device. (Baliga, 2018, p. 90)

During the breakdown event, as the voltage is high and the current increases, the power increases beyond the power dissipation capability of the device, eventually leading to thermal runaway in the active area of the chip. (Kelley et al., 2016)

The occurrence of avalanche breakdown has been met in the Flyback converter (i.e., typical example for avalanche mode of operation), where during the turn-off of the transistor, a high overvoltage can be induced by the magnetizing inductance of the transformer (McDonald et al., 2011, p. 4).

## 3 Avalanche ruggedness test

This chapter describes the test bench designed and built to study the avalanche ruggedness phenomenon of SiC power MOSFET. In addition, the procedure of how the investigated device is triggered into an avalanche event is discussed, as well as the electrical measurements performed during the event. Finally, the measurement equipment and the parts used in the test setup are presented.

#### 3.1 Test system

A test setup was designed and built to investigate the reliability of power MOSFETs AR. The purpose of the test setup is to enable robustness assessments of different MOS-FET suppliers. The test focuses mainly on device-level reliability. Typically, these tests are performed by the MOSFET suppliers to give the datasheet an energy value that the device can withstand during an avalanche event. However, the suppliers' datasheets reveal a considerably diverse amount of information on the avalanche robustness, and often are not mentioned at all. Especially when datasheets of SiC MOSFETs are considered the AR information is most often lacking. The main goal with the proposed AR test and testing scheme in this thesis is to get a unified overview of various suppliers' avalanche capabilities by comparing the maximum energy dissipation that the different devices can withstand in the avalanche mode.

The test setup built and used in this study is comparable with common AR tests. The device is in series with an inductor. The inductor has an inductance value L able to store up to ten times the MOSFETs datasheet rated avalanche energy  $E_{AV}$  for a given drain to source current  $I_{DS}$  and selected supply voltage  $V_{DC}$ . The supply voltage  $V_{DC}$  value shouldn't exceed the maximum rated drain to source voltage  $V_{DSmax}$  of the MOSFET. The gate voltage  $V_{GS}$  and gate resistance  $R_G$  used under the test are the ones recommended in the MOSFETs datasheet.

#### 3.2 Test description

By combining a power MOSFET in series with an inductive load, the AR of the device can be investigated. The combination of the device's high-speed switching and the inductive load causes a high surge voltage between the drain and source at the turn-off phase. This induced high voltage often exceeds the rated breakdown voltage  $V_{BR(DSS)}$ , which will trigger the device into avalanche mode. By the repetitive occurrence of the avalanche events, the qualification of the semiconductor device needs to be able to suppress (or survive) its datasheet specified avalanche energy  $E_{AV}$ , while keeping its characteristics after the test within datasheet specifications.

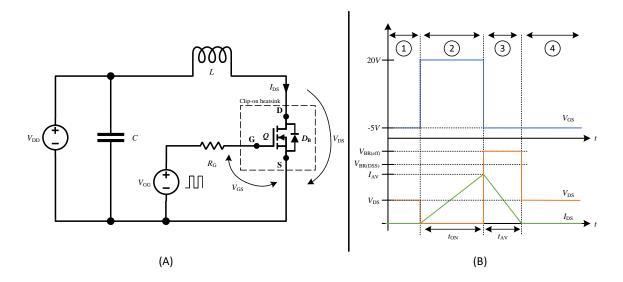

A standard test circuit for performing an AR test and its avalanche curves is shown in Figure 8. The device is mounted onto a TO-247-3 socket holder located on the test board. A clip-on heating sink is attached to the MOSFET. The device is seriesconnected with an inductor L, and the circuit branch is arranged in parallel with a DC capacitor C charged by a DC power supply  $V_{\rm DC}$ . A waveform generator controls the gate driver of the MOSFET. The avalanche energy  $E_{\rm AV}$  for the MOSFET in the circuit can be calculated as (Ionita et al., 2017):

$$E_{\rm AV} = \frac{1}{2} L I_{\rm AV}^2 \frac{V_{\rm BR(eff)}}{V_{\rm BR(eff)} - V_{\rm DC}},\tag{13}$$

where L is the inductance of the series inductor,  $I_{AS}$  is the peak avalanche current when the gate is turned off,  $V_{BR(eff)}$  is the effective avalanche breakdown voltage at peak discharge current, and  $V_{DC}$  is the supply voltage.

It is worth mentioning that  $V_{\text{BR(eff)}}$  must be higher than the MOSFETs breakdown voltage given in the device datasheet. Typically, the manufacturers implement a safety margin in their design. And as a rule of thumb, the effective breakdown voltage can be considered by the Equation (Renesas, 2015, p. 3; Berry et al., 2020, p. 105):

$$V_{\rm BR(eff)} \cong 1.3 * V_{\rm BR(DSS)},\tag{14}$$

where  $V_{\text{BR(eff)}}$  is the effective drain to source breakdown voltage at peak discharge current, and  $V_{\text{BR(DSS)}}$  is the rated drain to source breakdown voltage of the MOSFET.

Figure 8: Simplified circuit of an avalanche ruggedness test setup; (B) voltage and current waveforms during an avalanche breakdown event.

However, a more precise calculation for the avalanche energy  $E_{AV}$  can be obtained using the current and voltage measurements of the device by (McDonald et al., 2011, p. 9):

$$E_{\rm AV} = \int_{t_1}^{t_2} V_{\rm BR(eff)}(t) \times I_{\rm AS}(t) \times dt.$$

(15)

#### **3.3** Performing an avalanche event

As shown in Figure 8, performing a single avalanche event can be divided into four intervals. During the first interval, the MOSFET is OFF, no current or voltage flows through the device, and only the static supply voltage  $V_{\rm DC}$  is seen. The second interval starts as the gate driver is turned ON for a predefined on-time  $t_{\rm ON}$ . The current across the MOSFET starts to increase linearly to the desired test current according to the inductor L in series value and the supply voltage  $V_{\rm DC}$  at the rate defined by (Ionita et al., 2017):

$$\frac{di}{dt} = \frac{V_{\rm DC}}{L},\tag{16}$$

where  $V_{\rm DC}$  is the supply voltage, and L is the series inductor inductance.

The third interval starts as the gate driver is switched-off, which abruptly turns off the MOSFET. The turn-off of the MOSFET opens the circuit, and the energy built up in the inductor L will dissipate its stored energy into the device. This inductive current continues to flow, causing a high voltage across the drain to the source. This voltage passes the breakdown voltage  $V_{\text{BR(DSS)}}$  and is clamped to the effective breakdown voltage  $V_{\text{BR(eff)}}$  until the load current reaches zero. If the device passes the avalanche phase, the last and fourth interval begins. The effective breakdown voltage  $V_{\text{BR(eff)}}$ falls to the static level equivalent to the supply voltage  $V_{\text{DC}}$ , and the drain to source current  $I_{\text{DS}}$  falls to zero. This value  $I_{\text{AV}}$  should stay under or equal to the max rated continuous drain current  $I_{\text{D}}$  of the device.

#### **3.4** Measurements during an avalanche event

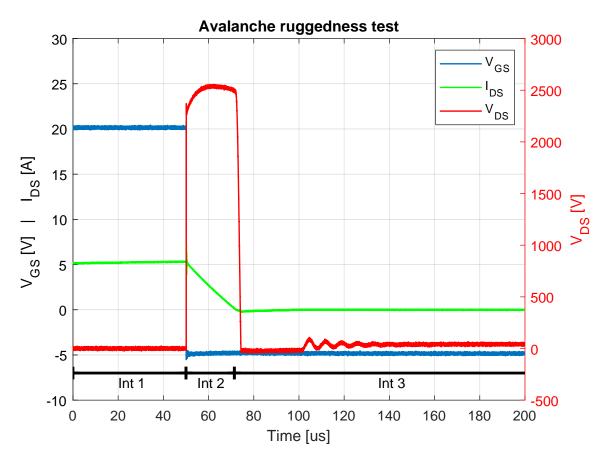

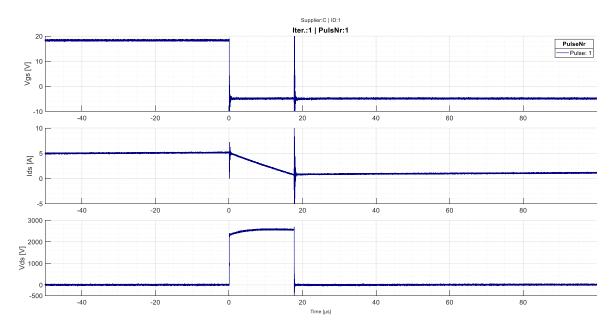

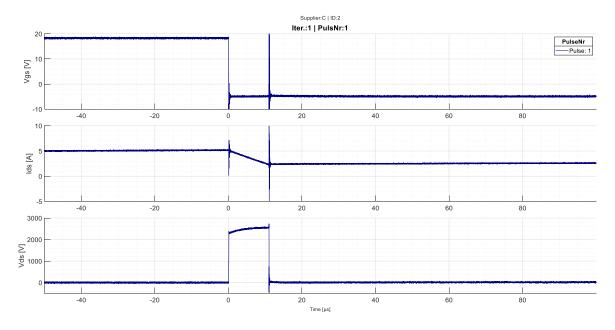

During the test, three quantities are measured with the help of an oscilloscope, as shown in Figure 9.

- 1. The first monitored parameter is the gate voltage  $V_{\rm GS}$  (blue waveform) measured between the MOSFETs gate and source. When switching the device ON, the voltage between  $V_{\rm GS}$  goes from -5V to 20V (interval 1) and then back to OFF state -5V (interval 2 and 3).

- 2. The second monitored parameter is the drain to source voltage  $V_{\rm DS}$  (red waveform). When the MOSFET changes the state from blocking to conducting, the drain to source voltage changes from  $V_{\rm DD}$  to zero (interval 1). When the  $t_{\rm ON}$ time has passed, and the device is switched-off, the voltage rises sharply above the breakdown voltage  $V_{\rm BR(DSS)}$  for a  $t_{\rm AV}$  time (interval 2). If the device survives the avalanche phase, the voltage reverts to the supply voltage  $V_{\rm DC}$  level (interval 3).

- 3. The third and last monitored parameter is the drain-source current  $I_{\rm DS}$  passing through the device (green waveform). The current increases linearly when the MOSFET is ON, and the maximum current  $I_{\rm AV}$  is reached when the MOSFET is switched off (interval 1). The drain to source current  $I_{\rm DS}$  decrease linearly back to zero (interval 2 and 3).

Figure 9: Waveforms of a SiC C2M1000170 MOSFET during avalanche. Drain to source voltage  $V_{\rm DS}$  (red), drain to source current  $I_{\rm DS}$  (green), and gate to source voltage  $V_{\rm GS}$  (blue).

## 3.5 Test bench

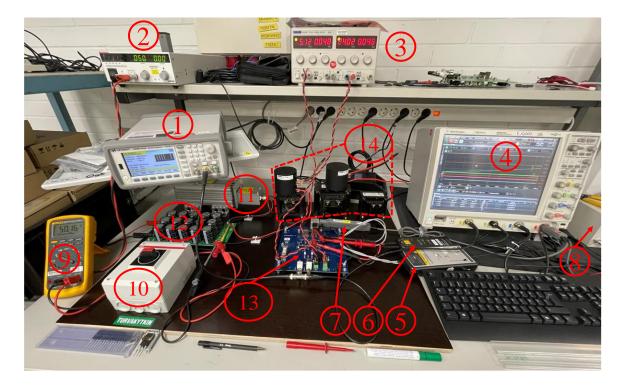

The test bench designed and built for the purpose of studying the avalanche ruggedness phenomenon of power MOSFETs in this thesis is shown in Figure 10.

Figure 10: Test bench for investigation of avalanche ruggedness in SiC MOSFETs.

The test bench consists of several components and measurement devices which are all listed in Table 1. The waveform generator is used to control the gate drive of the MOSFET. The waveform generator allows control of the device conduction time and the repetition rate of the pulses. The DC power supply is used as the main power supply for the test and is connected in parallel with a capacitor bank. The capacitor bank's main task is to store electrical energy and to provide a stable flow of this energy to the device under test. The triple power supply generates the different voltage levels for the main electronics on the AR test board. The oscilloscope is used to display and capture the current and voltage waveforms with the help of current and voltage probes attached to various terminals of the device. The test bench is also equipped with a safety circuit. The safety circuit consists of a manual switch, and a discharge resistor arranged parallel with the capacitor bank. When the switch is closed, the capacitor bank is discharged through the discharge resistor. The multimeter is also a part of the safety circuit. The multimeter is used for the voltage measurement between the capacitor bank's potentials and indicates if the voltage has decreased.

| ID | Device                       | Brand       | Model         | Function                                                                                                   |

|----|------------------------------|-------------|---------------|------------------------------------------------------------------------------------------------------------|

| 1  | Waveform<br>Generator        | Keysight    | 33500B Series | Control the gate<br>drive of the DUT                                                                       |

| 2  | DC Power Supply              | Sorensen    | XHR 600-1.7   | Main power supply<br>for the test                                                                          |

| 3  | Triple Power<br>Supply       | Aim-TTi     | EX345RT       | 5V and $24V$ for<br>the main electronics                                                                   |

| 4  | Mixed Signal<br>Oscilloscope | Agilent     | MSO9104A      | Capture the waveforms<br>during an AR event                                                                |

| 5  | Differential<br>Probe        | Yokogawa    | 701926        | $\begin{array}{c} \text{Measure the drain} \\ \text{to source } V_{\text{DS}} \text{ voltage} \end{array}$ |

| 6  | Differential<br>Probe        | Tektronix   | P5200A        | $\begin{array}{c} \text{Measure the gate} \\ \text{to source } V_{\text{GS}} \text{ voltage} \end{array}$  |

| 7  | Current<br>Probe             | Yokogawa    | 701933        | $\begin{array}{c} \text{Measure the drain} \\ \text{to source } I_{\text{DS}} \text{ current} \end{array}$ |

| 8  | Power Supply                 | Yokogawa    | 701934        | Power supply to<br>the current probe                                                                       |

| 9  | Multimeter                   | Fluke       | 87V TRMS      | Measure the voltage<br>across the capacitor bank                                                           |

| 10 | Safety Switch                | ABB         |               | Switch to discharge the<br>capacitor bank                                                                  |

| 11 | Discharge<br>resistor        |             |               | Resistor to discharge<br>the capacitor bank                                                                |

| 12 | Capacitor bank               | Self-design |               | Capacitor bank for<br>AR tests                                                                             |

| 13 | AR Test board                | Self-design |               | Avalanche ruggedness<br>test board                                                                         |

| 14 | Inductors                    |             |               | Different size inductors<br>used in the test                                                               |

Table 1: Equipment used for the AR test bench.

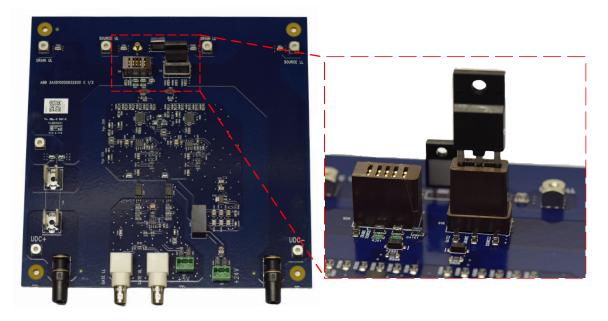

The test board designed to examine the AR of the SiC MOSFETs is shown in Figure 11. The test board is designed to test the TO-247-3 and TO-247-4 package devices. The primary voltages are derived on the edges of the PCB, and the gate driver circuit and its auxiliary voltages are found in the center of the PCB. A more detailed block diagram of the AR test bench can be found in the Appendix 1.

Figure 11: The designed test bench with the gate driver circuit for investigation of avalanche ruggedness in SiC MOSFETs.

## 4 Avalanche ruggedness test procedure

This chapter describes the implemented avalanche ruggedness test procedure for SiC MOSFETs. The measurement equipment used to investigate the aging effect on the devices, as well as how to set the aging parameters for the DUTs, is also described.

#### 4.1 Implemented test procedure

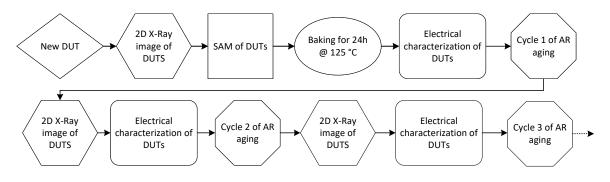

Figure 12 illustrates the test procedure implemented to investigate the avalanche ruggedness of SiC MOSFETs. The test procedure consists of four main steps: X-ray image of the DUTs, Scanning Acoustic Microscopy (SAM) of the DUTs, electrical characterization of the DUTs, and the AR test for the DUTs.

Figure 12: Implemented test procedure for investigation of the avalanche ruggedness of SiC MOSFETs.

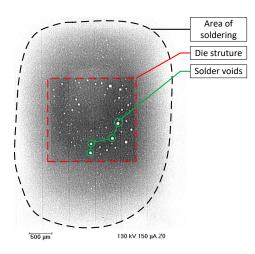

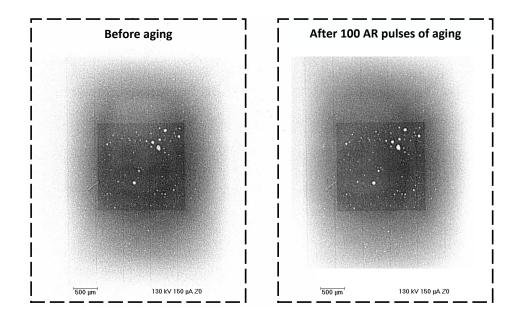

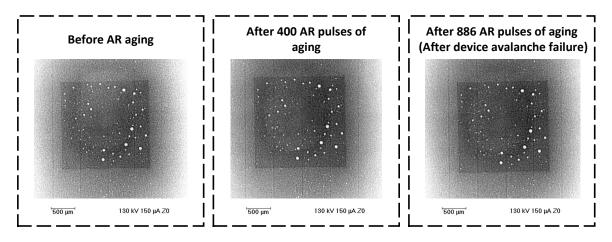

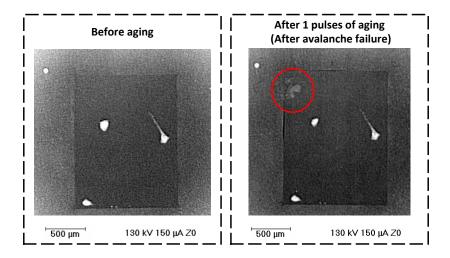

Before the first cycle of the AR test, the initial conditions of the DUTs needs to be determined. The determination of the initial condition of the DUTs is performed by the imaging and electrical characterization of the DUTs, as shown in Figure 12. The first step of the characterization for the DUTs is done with a 2D X-ray machine. An example of an X-ray image of a SiC MOSFET chip is shown in Figure 13.

Figure 13: X-ray image of a C2M1000170D SiC MOSFET.

The X-ray image is taken from the top side of the DUT. The X-ray image is used to evaluate the soldering area, the die structure, and solder voids in the structure, as shown in Figure 13. The bond wires between the chip and the leeds absorb too few X-rays to create noticeable contrast, and they can not be observed in the X-ray image.

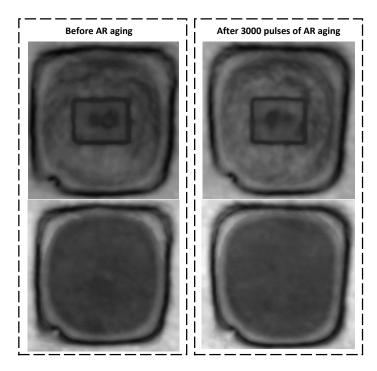

In the second step, the DUTs are imagined using a SAM. The SAM image of the DUT can efficiently reveal physical defects such as cracks, voids, and delamination in between the different attached layers. The SAM images of the DUTs are taken before the first cycle of the AR test and after the breakdown of the DUT. Figure 14 shows a SAM image of three layers: System solder of die-attach, chip die structure, and bond wire attached to the top of the chip die.

Figure 14: SAM images of a C2M1000170D SiC MOSFET. From left to right: System solder of die-attach, chip die structure, and bond wires attached to the top of the chip die.

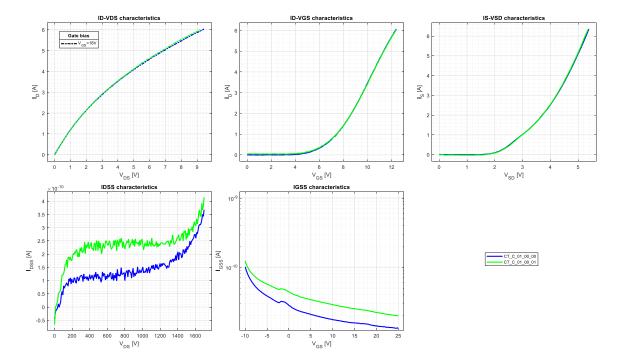

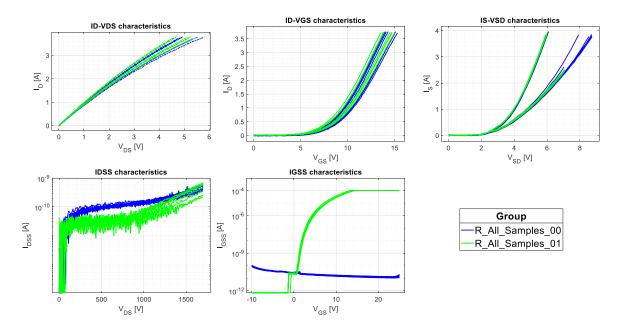

The third and last step of the initial condition characterization is the electrical characterization of the DUTs. Before the electrical characterization can be performed, the DUTs are baked for 24 hours in a thermal chamber at 125 degrees Celsius accor-

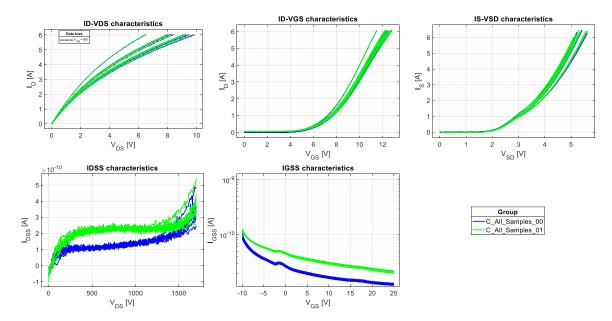

ing to JEDEC standard 22-A113D, to drive out any leftover moisture from the SAM process from the samples before any electrical stress is applied to the DUTs. The electrical characterization is performed with a power device analyzer. This device allows the measurement of five key electrical characteristic measurements to reveal potential degradation of the DUT. The electrical characterization measurements are as follows: Output characteristics  $I_{\rm D}$ - $V_{\rm DS}$ , transfer characteristics  $I_{\rm D}$ - $V_{\rm GS}$ , forward characteristics of the body diode  $I_{\rm S}$ - $I_{\rm SD}$ , drain-source leakage current  $I_{\rm DSS}$ , and the gate-source leakage current  $I_{\rm GSS}$ . The five electrical characterizations measurements are shown in Figure 15.

Figure 15: Five electrical characterization measurements were performed with a Keysight power device analyzer model B1506A. The blue-colored lines are measurements performed before any AR test, and the green-colored lines are measurements performed after 100 aging pulses of AR for the same DUT.

The imaging and electrical characterization devices used in the test procedure are listed in Table 2.

Table 2: Measurement equipment used for investigation of the aging effect in SiC MOSFETs.

| Device                   | Brand            | Model               |  |  |

|--------------------------|------------------|---------------------|--|--|

| X-ray Machine            | General Electric | Nanomex 180 DXR     |  |  |

| Scanning Acoustic        | Sonoscan         | GEN6 C-SAM Acoustic |  |  |

| Microscope               | Sonoscan         | Microscope          |  |  |

| Thermal Chamber          | Espec            | SH-642              |  |  |

| Power Device<br>Analyzer | Keysight         | B1506A              |  |  |

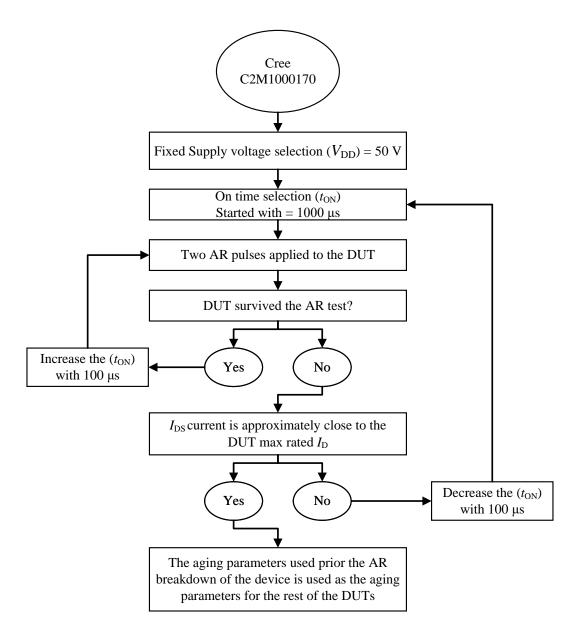

### 4.2 Setting the aging parameter values

For the AR test performed in this thesis, one device from each supplier was selected to find the End-of-Life (EoL) avalanche energy. For each supplier, the maximum dissipated avalanche energy for the device was discovered by increasing the  $t_{\rm ON}$  while the  $V_{\rm DC}$  for the test was held constant. The  $t_{\rm ON}$  was increased with 100  $\mu$ s steps until avalanche failure of the device was reached. Two avalanche pulses with a repetition rate of 1 Hz were given for each step. Once the failure occurred, the parameters used prior to the device's destruction were considered the avalanche energy the device could withstand. These parameter values were then used for the aging of the DUTs selected for the AR tests. Figure 16 shows the procedure to find the aging parameter values for Cree C2M1000170 SiC MOSFET.

Figure 16: The method to find the aging parameter values for Cree C2M1000170 SiC MOSFET

### 5 Analysis and results

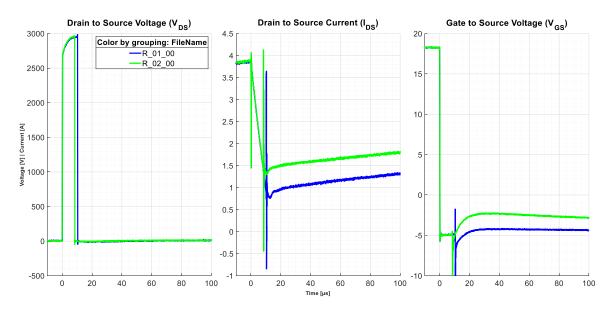

The analysis and results of the AR test conducted on two TO-247-3 packaged SiC power MOSFET suppliers is presented in this chapter. Both suppliers' devices benchmarked are 1700V rated SiC planar MOSFETs. For the respective supplier, ten DUTs were selected for AR testing. The datasheet values for the devices of each supplier are presented in the Table 3.

| Supplier                      | Cree        | Rohm      |

|-------------------------------|-------------|-----------|

| Part Number                   | C2M1000170D | SCT2H12NZ |

| Generation                    | 2nd Gen     | 2nd Gen   |

| $V_{\rm DS}$ (V)              | 1700        | 1700      |

| $I_{\rm D}(A)$                | 5           | 3.7       |

| $T_{\text{jmax}} (^{\circ}C)$ | 150         | 175       |

| $R_{\rm DS(on)}(\Omega)$      | 1           | 1.15      |

Table 3: Datasheet values for the tested DUTs. (Cree, 2021; ROHM, 2017)

#### 5.1 Cree C2M1000170

As described at the end of Section 4, the maximum dissipated avalanche energy for the Cree C2M1000170 devices was obtained using the parameters listed in Table 4.

| Cree C2M1000170                     |      |       |       |       |      |

|-------------------------------------|------|-------|-------|-------|------|

| Measurement identification          | 001  | 002   | 003   | 004   | 005  |

| number (ID)                         |      |       |       |       |      |

| Supply voltage $V_{\rm DC}$         | 50   | 50    | 50    | 50    | 50   |

| $t_{\rm ON}$ time ( $\mu s$ )       | 1000 | 1100  | 1200  | 1300  | 1400 |

| Avalanche energy (mJ)               | 86.7 | 102.9 | 119.7 | 137.2 | -    |

| Survived the AR test<br>(PASS/FAIL) | PASS | PASS  | PASS  | PASS  | FAIL |

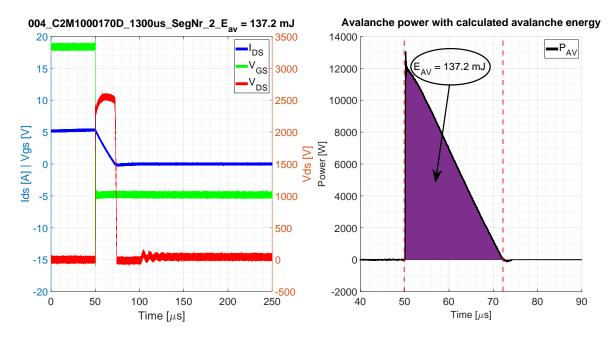

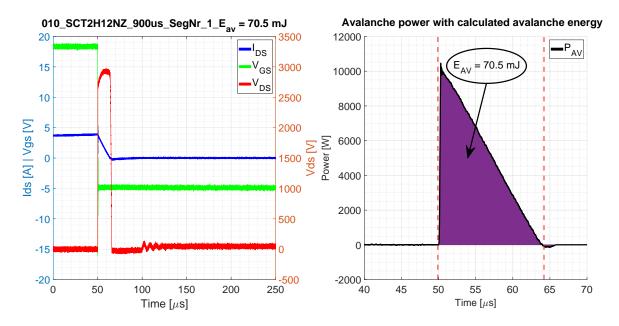

The DUT failed with parameter values:  $V_{\rm DC} = 50 V$ , and  $t_{\rm ON} = 1400 \ \mu$ s. The last recorded step before avalanche breakdown of the DUT was with the following parameter values:  $V_{\rm DC} = 50 V$  and  $t_{\rm ON} = 1300 \ \mu$ s, which using Equation 15, corresponds to the avalanche energy of  $E_{\rm AV} = 137 \ \text{mJ}$ . Figure 17 shows the waveforms with these parameter values.

Figure 17: On the left-hand side is the last recorded AR pulse for the Cree C2M1000170 SiC MOSFET, and on the right-hand side, the avalanche power with calculated avalanche energy.

For the ten Cree C2M1000170 samples selected for the AR test, the final aging parameters used were with  $V_{\rm DC} = 50 V$  and  $t_{\rm ON} = 1200 \ \mu$ s, corresponding to an avalanche energy of ~120 mJ. Before the AR test with the final aging parameters were applied to the ten selected DUTs, it was decided to do a pre-conditioning test for all ten DUTs. This was done to ensure all devices were functional and to disclose any early failures of the DUTs. The pre-conditioning test were performed with  $V_{\rm DC} = 50 V$  and  $t_{\rm ON} = 1100 \ \mu$ s corresponding to  $E_{\rm AV} = 102.9 \ \text{mJ}$  per pulse. The same repetition rate of 1 Hz was used for the pre-conditioning stage. All ten DUTs survived the pre-aging stage, and no device breakdown did occur. After the AR pre-conditioning, the electrical re-characterization for the DUTs was made.

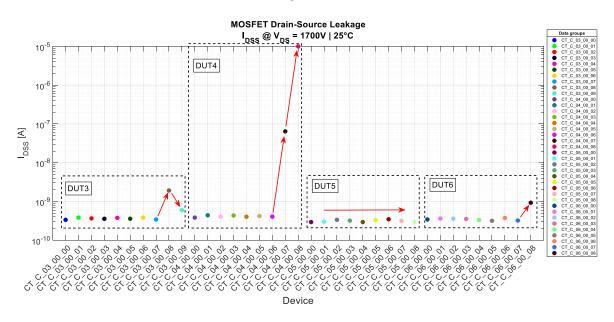

The electrical characterization measurement results revealed that after the first 100 AR pre-conditioning pulses, the drain to source leakage current  $I_{\text{DSS}}$  increased approximately twice in value for the measurement range of  $V_{\text{DS}} = 250 V$  to 800 V compared to the  $I_{\text{DSS}}$  characterization measurement performed before the AR test. An increase in the gate to source leakage current  $I_{\text{GSS}}$  is seen for the full measurement range. No significant changes were seen in the rest of the electrical characterization measurements  $(I_{\text{D}}-V_{\text{DS}}, I_{\text{D}}-V_{\text{GS}}, \text{ and } I_{\text{S}}-V_{\text{SD}})$ . Figure 18 shows the electrical characterization measurement

ment results for the ten DUTs. The blue line shows the measurement performed before the pre-conditioning test, and the green line indicates the measurement performed after the first 100 AR pre-conditioning pulses where the  $E_{\rm AV}$  was  $\approx 100$  mJ per pulse.

Figure 18: Electrical characterization measurement results before and after the 100 aging pulses. The  $E_{\rm AV}$  was  $\approx 100$  mJ per pulse. Green-colored lines are before any AR aging pulses, and the blue-colored lines are after 100 AR aging pulses were applied to the DUTs.

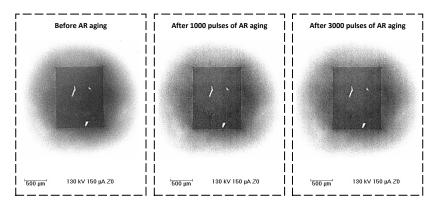

After the electrical characterization, the 2D-Xray inspection of the ten Cree DUTs was performed. From the X-ray images, no changes in the construction could be observed after the 100 aging pulses. Figure 19 shows one X-ray image taken from the top side of the DUT.

Figure 19: Cree C2M1000170 - DUT1 2D X-ray images after 100 aging pulses.

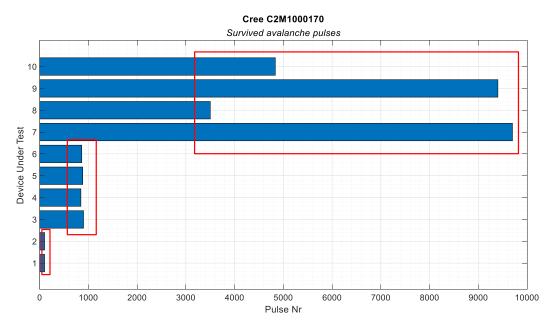

After the pre-conditioning stage, the AR test was continued with the aging parameters of  $V_{\rm DC} = 50 V$  and  $t_{\rm ON} = 1200 \ \mu$ s, corresponding to the  $E_{\rm AV}$  of  $\approx 120$  mJ. The total amount of survived aging pulses for all ten DUTs from Cree is shown in Figure 20. The figure shows that the DUTs from Cree have a notable variance in the robustness against AR aging pulses, where some of the DUTs survive 100, and some DUTs survive several thousand AR aging pulses. From the figure, three distinct groups can clearly be seen, indicating that the devices failed into three different types of failures.

Figure 20: Total survived AR aging pulses for each DUT from Cree.

As seen in Figure 20, the first avalanche failures occurred for the DUTs with the identifier (ID) 1 and 2. Both devices failed on the first AR pulse of the first iteration and survived for a total of 100 pre-conditioning pulses. Figure 21 shows the oscilloscope waveforms during failure for DUT1, and Figure 22 for DUT2.

Figure 21: Oscilloscope waveforms of the failed Cree DUT1. From top to bottom:  $V_{\rm GS}$ ,  $I_{\rm DS}$ , and  $V_{\rm DS}$ .

Figure 22: Oscilloscope waveforms of the failed Cree DUT2. From top to bottom:  $V_{\text{GS}}$ ,  $I_{\text{DS}}$ , and  $V_{\text{DS}}$ .

From Figures 21 and 22, it is seen that both DUT1 and DUT2 have almost a similar breakdown phenomenon. For the DUT1, the drain to source current  $I_{\rm DS}$  goes from ~ 5.1 A down to ~ 0.7 A until the failure occurs. The avalanche time  $t_{\rm AV}$  before breakdown is  $\approx 17.7 \ \mu$ s. When the DUT fails ( $t_{\rm AV} \approx 17.7 \ \mu$ s), the  $I_{\rm DS}$  current is not extinguished and does not reach zero as it should. Furthermore, a fluctuation in the  $V_{\rm GS}$  voltage is seen even if the  $V_{\rm GS}$  applied to the device is -5 V. From the  $V_{\rm DS}$  waveform it is seen that the effective avalanche breakdown voltage  $V_{\rm (BR)eff}$  stays at  $\approx 2600 V$  for the time before the breakdown ( $t_{\rm AV} \ 0$  to 17.7  $\mu$ s). When the failure occurs at  $t_{\rm AV} = 17.7 \ \mu$ s, the  $V_{\rm (BR)eff}$  rises to 2700 V and drops down to the input voltage level  $V_{\rm DC}$  of 50 V.

The DUT2 behaves almost identical to the DUT1. The difference between the DUT2 compared to the DUT1 is that the avalanche time before device breakdown is shorter,  $t_{\rm AV} = 11 \ \mu$ s. The device breakdown occurs at ~ 2.3 A. The  $V_{\rm GS}$  and  $V_{\rm DS}$  profiles behave similarly for the DUT2 as for the DUT1. The resistance measured between the different terminals for both DUTs are almost identical as seen in Table 5.

Table 5: Resistances between the different terminals after the avalanche breakdown.

|                                    | Cree C2M1000170 |       |

|------------------------------------|-----------------|-------|

| Measurement                        | DUT1            | DUT2  |

| Gate-source resistance $(\Omega)$  | 229.2           | 224.5 |

| Gate-drain resistance $(\Omega)$   | 251.2           | 235.6 |

| Drain-source resistance $(\Omega)$ | 22.8            | 11.5  |

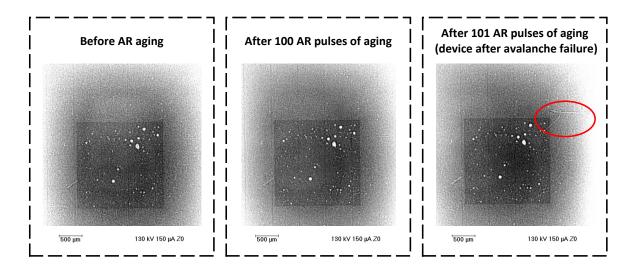

The 2D X-ray images of DUTs 1 and 2 do not show differences in the chip structure compared to the X-ray image taken before the AR testing. Figure 23 shows X-ray images taken before and after the avalanche breakdown of the DUT1. The red circle in the picture on the right-hand side shows a mechanical scratch from the fastening of the DUT to the heatsink.

Figure 23: Cree C2M1000170 - DUT1 2D X-ray images. From left to right: X-ray image before any aging. X-ray image after the pre-conditioning stage and X-ray image after the avalanche breakdown.

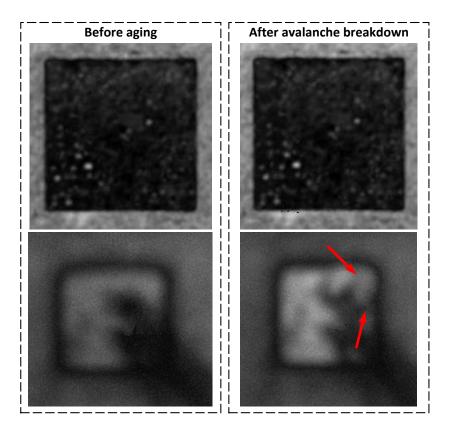

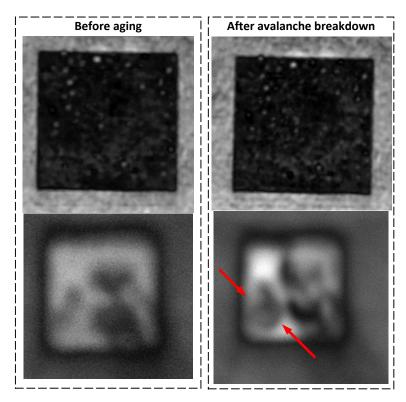

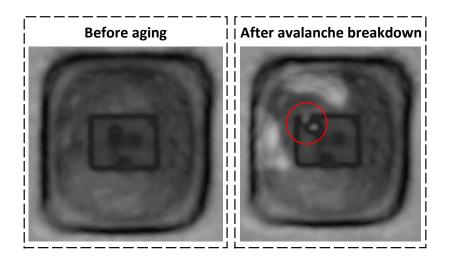

After the X-ray examination, a SAM analysis of the DUTs was made. For the DUTs from Cree, the SAM images were taken from the top and bottom sides of the devices. Figure 24 shows the SAM images taken of the DUT1. The image on the upper left-hand side is a SAM image of the die-attach layer from the bottom side of the device, whereas the image below is from the top side of the device and shows the bond wires attached to the top of the chip. Both images are taken before any AR aging. The SAM images on the right-hand side are taken after the avalanche breakdown of the DUT1. From the upper image, any variance is not noticed in the SAM image, and it can be stated that for this DUT1, the AR has not affected the die-attach layer. From the bottom SAM image, a possible failure location on the chip can be detected, and the location is marked with red arrows. The removal of the mold compound reveals the failure location on the chip and is shown in Figure 25.

Figure 24: Figure 24 Cree C2M1000170 - DUT1 SAM images. On the left-hand side is the image taken before aging and on the right-hand side is the image taken after the avalanche breakdown. The red arrows indicate a possible failure location.

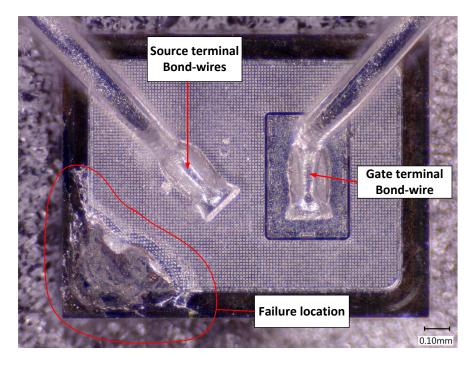

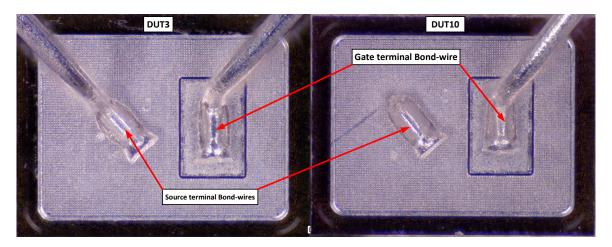

Figure 25: Failure location of the Cree DUT1 after the avalanche breakdown.

Regarding the second failure group identified in Figure 26, all four DUTs 3-6 sur-

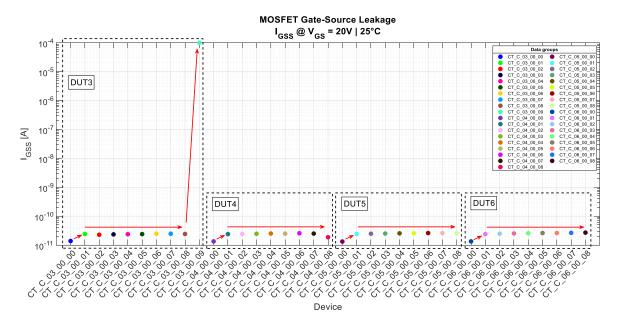

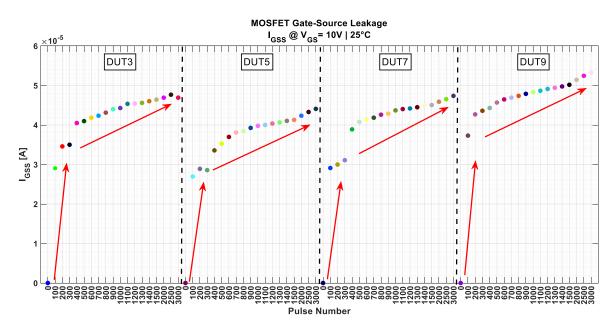

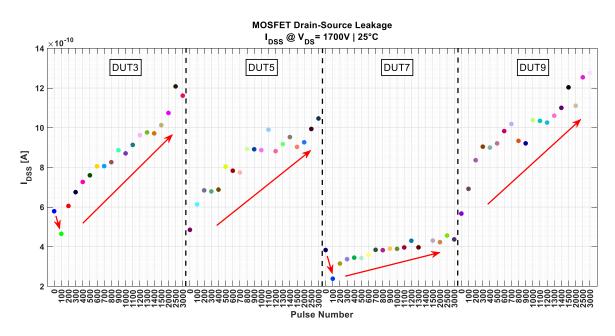

vived for  $\approx 900$  aging pulses. The figure shows a scatter plot of  $I_{\rm DSS}$  characterization measurement completed after every 100 AR aging pulses applied to the DUTs. The figure reveals that DUT3, DUT4, and DUT6 behave similarly. The  $I_{\rm DSS}$  begins to increase before the failure of these DUTs occurs. For the DUT5, any significant change in the  $I_{\rm GSS}$  is not seen before the breakdown of the device. The  $I_{\rm GSS}$  characterization measurement was also performed for the DUTs and is shown in Figure 27. The figure shows that the  $I_{\rm GSS}$  rises after the first 100 AR aging pulses but does not increase significantly for any of the pulses given to the DUTs after that. The DUT3 did not degrade completely after the 900 AR aging pulses, and it was possible to electrically re-characteristics. The DUT4 to 6 failed in the AR test, and they were not possible to be electrically re-characteristic. The  $I_{\rm GSS}$  for DUT3 after 900 AR aging pulses was greater than 100  $\mu A$ , which was set as the maximum limit for  $I_{\rm GSS}$  measurement, and this DUT was chosen for further investigation.

Figure 26: Drain to source leakage current plot for DUTs 3 to 6. The  $I_{\text{DSS}}$  measurement was performed after every 100 AR aging pulses. The 00 data point is before any aging pulses, and for example, the 05 data point is after 500 AR aging pulses. The  $I_{\text{DSS}}$  value is taken at  $V_{\text{DS}} = 1700 \ V$ .

Figure 27: Drain to source leakage current plot for DUTs 3 to 6. The  $I_{\text{GSS}}$  measurement was performed after every 100 AR aging pulses. The 00 data point is before any aging pulses, and for example, the 05 data point is after 500 aging pulses. The  $I_{\text{GSS}}$  value is taken at  $V_{\text{GS}} = 20$  V.

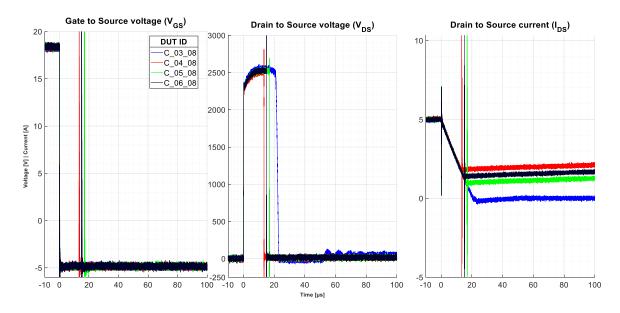

The oscilloscope measurements during the AR test did not reveal any significant difference for the DUTs 4-6. The  $t_{\rm AV}$  varies for the DUTs as well as the number of pulses before the failure occurs. However, any notable difference in the voltage and current waveforms is not seen. Figure 28 shows the pulse where the avalanche breakdown occurs for the DUTs. This figure shows that the breakdown behaviour for these DUTs is similar to those of DUT1 and 2. The  $I_{\rm DS}$  current is not extinguished and does not reach zero as it should. Furthermore, a fluctuation in the  $V_{\rm GS}$  voltage is seen even if the  $V_{\rm GS}$  applied to the device is -5 V.

Figure 28: Oscilloscope waveforms of the failed Cree DUT3-6. From left to right:  $V_{\text{GS}}$ ,  $V_{\text{DS}}$ , and  $I_{\text{DS}}$ . Blue colored lines are the waveforms for DUT3, red for DUT4, green for DUT5 and black for DUT6.

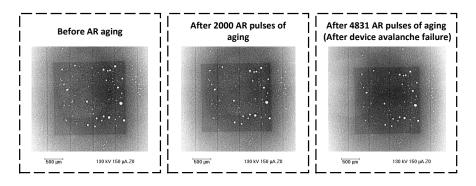

The X-ray investigation of the DUTs 3-6 did not reveal any abnormalities. Figure 29 shows X-ray images taken from the top side of the DUT5. Any notable change in the structure nor in the voids can be observed.

Figure 29: 2D X-ray image of the DUT5.

The SAM analysis of the DUT5 revealed similar results as the DUT1, although the DUT5 survived for almost  $\sim 8$  times more AR aging pulses. The SAM images of DUT5 are shown in Figure 30, and from the image, it can be stated that the AR aging pulses do not affect the die-attach layer even if the number of aging pulses increases. The SAM image taken from the top side of the DUT5 shows a possible failure location close to

one of the source bond wires and is marked with a red arrow. The mold compound was removed from the DUT5, and the failure location of the DUT5 is shown in Figure 31. The failure location for the DUT5 is clearly in the device's active area and is most likely a different failure mode than for the DUT1. Furthermore, one of the four source bond wires has been cut off close to the end termination of the wire. However, it is noted that this could result from the mold compound removal process and needs further investigation.

Figure 30: Cree C2M1000170 – DUT5 SAM images. On the left-hand side is the image taken before aging and on the right-hand side is the image taken after the avalanche breakdown. The red arrows indicate a possible failure location.

Figure 31: Failure location of the Cree DUT5 after the avalanche breakdown.

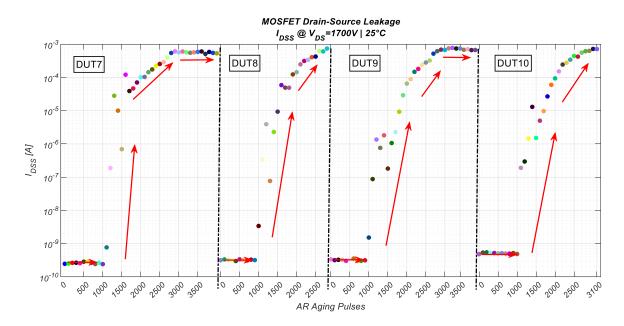

The subsequent AR breakdown occurred for DUT7, DUT8, DUT9, and DUT10. All four DUTs survived for several thousand AR aging pulses.

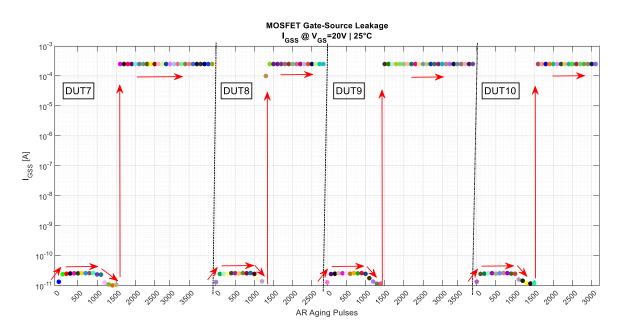

The electrical characteristics performed after every aging iteration reveals interesting behavior in the  $I_{\text{DSS}}$  and  $I_{\text{GSS}}$  measurements carried from the DUTs. The  $I_{\text{DSS}}$ results for DUTs 7 to 10 are shown in Figure 32 and the  $I_{\text{GSS}}$  in Figure 33. From the  $I_{\text{DSS}}$  figure, it can be noticed that all four DUTs behave similarly. The  $I_{\text{DSS}}$  stays at almost the same level for the first thousand AR aging pulses, after which the  $I_{\text{DSS}}$ starts to rise. The  $I_{\text{GSS}}$  also behaves identically to the previously analyzed DUTs 1-6. The  $I_{\text{GSS}}$  increases after the pre-conditioning stage, whereafter the  $I_{\text{GSS}}$  stays at the same level for approximately one thousand AR aging pulses, after which the  $I_{\text{GSS}}$  starts to decline. The  $I_{\text{GSS}}$  descends for about ~ 400 pulses before the  $I_{\text{GSS}}$  rapidly increases above the 250  $\mu A$ , which was set as the maximum limit for  $I_{\text{GSS}}$  measurement. Furthermore, the relation between the  $I_{\text{DSS}}$  starts to increase, the  $I_{\text{GSS}}$  starts to decrease.

Figure 32: Drain to source leakage current plot for DUTs 7-10. The  $I_{\text{DSS}}$  measurement was performed after every 100 AR aging pulses. The  $I_{\text{DSS}}$  value is taken at  $V_{\text{DS}} = 1700$  V.

Figure 33: Gate to source leakage current plot for DUTs 7-10. The  $I_{\text{GSS}}$  measurement was performed after every 100 aging pulses. The  $I_{\text{GSS}}$  value is taken at  $V_{\text{GS}} = 20$  V.

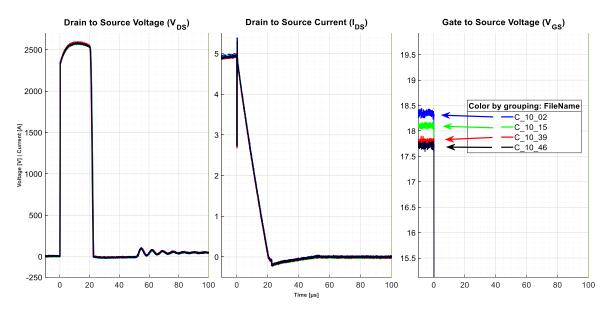

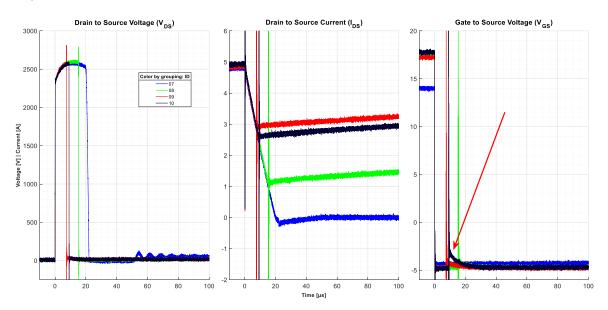

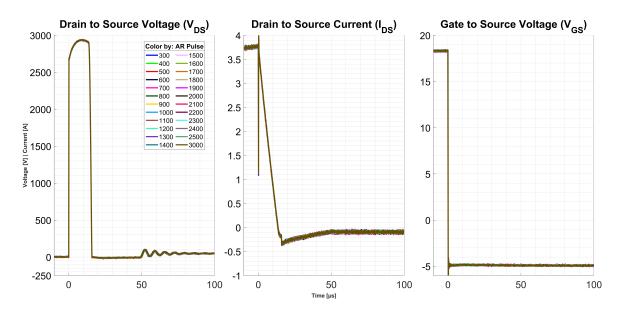

The oscilloscope measurements during the AR test did show some differences for the DUTs 7 to 10 compared to the DUTs 1 to 6. The most notable difference for these DUTs that survived for several thousand AR aging pulses is that the  $V_{\rm GS}$  declined as more AR aging pulses were applied to the DUTs. Figure 33 shows that when the  $I_{\text{GSS}}$  starts to leak 250  $\mu A$  at 1600 AR aging pulses for the DUT10, the impact is also seen in the AR tests. Figure 34 shows the oscilloscope waveforms during the AR tests to the DUT10. This figure shows every 100 AR aging pulse applied to the device. The blue-colored line is when 300 AR aging pulses are applied, and the green-colored line is when 1600 AR aging pulses were applied to the DUT. Any notable difference in the oscilloscope waveforms between the 300 to 1600 AR pulses is not seen, whereas when the device's gate starts to leak over 250  $\mu A$ , the  $V_{\text{GS}}$  during the AR test starts to decline. When further AR aging pulses are applied to the DUT, the  $V_{\text{GS}}$  decline until the device breakdown occurs at ~ 4800 AR aging pulses.

Figure 34: Oscilloscope waveforms of the Cree DUT10. From left to right:  $V_{\rm DS}$ ,  $I_{\rm DS}$ , and  $V_{\rm GS}$ . The blue line shows the 300 AR aging pulse, the green line shows the 1600 AR aging pulse, the red line shows the 4000 AR aging pulse, and the black line shows the 4700 AR aging pulse.

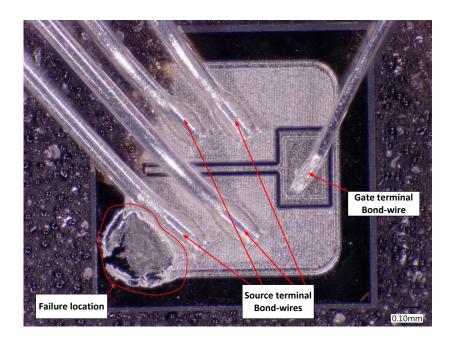

The X-ray investigation of the DUTs 7 to 10 did not show any abnormalities. Figure 35 shows X-ray images taken from the top side of the DUT10. From the figure, it can be concluded that the AR aging pulses do not affect the chip soldering, and any changes in the solder voids do not occur even if thousands of AR aging pulses are applied to the DUTs. Furthermore, the X-ray inspection of the Cree DUTs does not reveal any failure location on the DUTs, and therefore the X-ray is not an ideal technique for finding the damaged location in the CREE 1700 V rated MOSFETs.

Figure 35: 2D X-ray image of the DUT10.

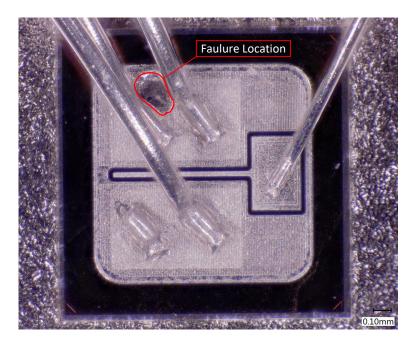

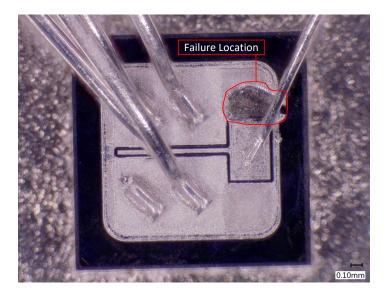

The SAM analysis of the DUT10 shows that the breakdown occurred close to the gate terminal of the device. The failure spot is shown in Figure 36, and the red arrow points to the breakdown location on the chip. After the SAM analysis of DUT10, the mold compound was removed, and an optical microscope image of DUT10 is shown in Figure 37. The mold compound removal proves that the breakdown of the device has occurred close to the gate terminal of the device chip and reveals a third failure mode for the Cree 1700 V devices.

Figure 36: Cree C2M1000170 – DUT10 SAM images. On the left-hand side is the images taken before aging and on the right-hand side is the image taken after the avalanche breakdown. The red arrows indicate the failure location of the DUT.

Figure 37: Failure location of the Cree DUT10 after the avalanche breakdown.

Figure 38 shows the AR aging pulse where the DUTs breakdown occures. From this figure, it can be noticed that for the DUTs 8 to 10, a slight voltage rise in the  $V_{\rm GS}$ appears when the device failure occurs. This rise is not seen for the DUTs 1 to 6 and furthermore supports that these devices that last for several thousand AR aging pulses fail in a different way than the ones that last only hundreds of AR aging pulses. The  $I_{\rm DS}$  and  $V_{\rm DS}$  waveforms for the DUTs 7 to 10 are similar to the rest of the DUTs, and any notable difference are not seen.

Figure 38: Oscilloscope waveforms during the AR aging of the failed Cree DUT10. From left to right:  $V_{\rm DS}$ ,  $I_{\rm DS}$ , and  $V_{\rm GS}$ . The red arrow indicates the rise in the  $V_{\rm GS}$  waveform.

#### 5.2 Summary of the Cree C2M1000170 devices

In the AR aging test performed in this thesis, three different failure modes could be observed for the Cree C2M1000170 MOSFETs. The first failure mode occurred for DUTs 1 to 2. The failure for these DUTs occurs in the chip's edge termination region (Figure 25). Since these devices failed at the first aging pulse, the likely hypothesis for the cause of failure seems to be defective edge termination structure, or possible contaminants. However, to disclose the true root cause of these failures, further failure analysis is required and is beyond the scope of this thesis.

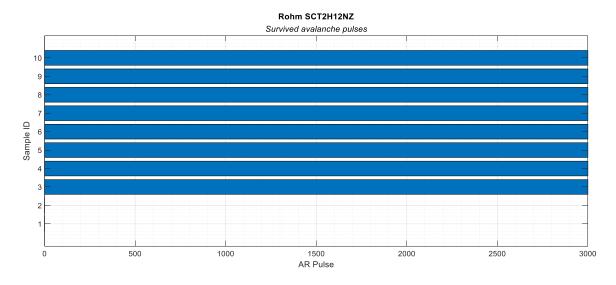

For the second failure mode observed with the DUTs 4 to 6, the failure spot is located in the active area of the chip (Figure 31). Since the failure spot is in the active region, the likely hypothesis for the true failure root cause is thermal runaway due to chip degradation from repetitive exposure to high avalanche energies. Which is also the expected root cause of the failure in AR testing. (Kelley et al., 2016)